题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

一个11位左移移位寄存器和两个同步时序电路相连,如图4-56(a)所示。这两个同步时序电路的状态如图4

一个11位左移移位寄存器和两个同步时序电路相连,如图4-56(a)所示。这两个同步时序电路的状态如图4-56(b)所示。设寄存器的状态为01101000100,两个时序电路均处于00状态,试确定在11个CP脉冲作用下Z2的输出序列。

.jpg)

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

一个11位左移移位寄存器和两个同步时序电路相连,如图4-56(a)所示。这两个同步时序电路的状态如图4-56(b)所示。设寄存器的状态为01101000100,两个时序电路均处于00状态,试确定在11个CP脉冲作用下Z2的输出序列。

.jpg)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“一个11位左移移位寄存器和两个同步时序电路相连,如图4-56…”相关的问题

更多“一个11位左移移位寄存器和两个同步时序电路相连,如图4-56…”相关的问题

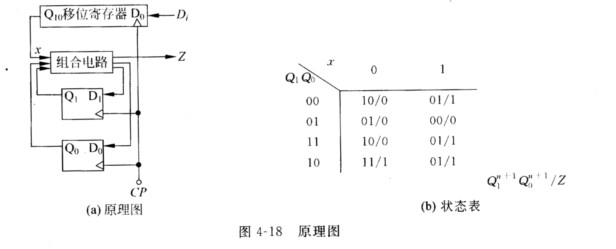

图4-18电路由一个11位移位寄存器和时序电路构成,移位寄存器寄存信息11 000011101且自右向左移位输出串行信号x,作用到时序电路输入端,再对外输出x。时序电路状态表如图4-18(b),初态00,试作出时序电路状态输出Q1、Q2和外输出z波形图。

试用J-K触发器构成一个三位移位寄存器,它在两个控制信号x1和x2的作用下实现表5-24所示的功能。

表5-24 功能表 | ||

x1 | x2 | 功能 |

0 | 0 | 保持 |

0 | 1 | 右移 |

1 | 0 | 左移 |

1 | 1 | 置零 |

设计一个同步时序逻辑电路,给出设计过程,它有两个输入X1、X2和一个输出Z,当X1、X2连续两次以上一致时输出为1,甭则输出为0。

如图所示电路由74194、74153和与非门组成。74194是双向移位寄存器,A~D为并行数码输入端,QA~QD为并行数码输出端,SLSI为左移串行输入端,SRSI为右移串行输入端;74153是双4-IMUX(数据选择器),地址(选择)输入端A、B公用,其函数表达式为:

A、1011--0110--1100--1000--0000

B、1011--0101--0010--0001--0000

C、1011--1100--1101--1110--1111

D、1011--1010--1001--1000--0111