更多“试用集成计数器74LSl63和8选1 MUX构成010011…”相关的问题

更多“试用集成计数器74LSl63和8选1 MUX构成010011…”相关的问题

第2题

试用集成4位二进制加法计数器74LS161构成十一进制计数器。 (1)用反馈复位法实现。 (2)用反馈置数法实现。

试用集成4位二进制加法计数器74LS161构成十二进制计数器。

(1)用反馈复位法实现。

(2)用反馈置数法实现。

第3题

试用JK触发器设计一个变模计数器,要求: (1)控制端X=0时,计数器的模M=3,计数规律为

试用JK触发器设计一个变模计数器,要求: (1)控制端X=0时,计数器的模M=3,计数规律为

1.jpg) (2)控制端X=1时,计数器的模M=4,计数规律为

(2)控制端X=1时,计数器的模M=4,计数规律为

2.jpg) 试画出逻辑电路图。

试画出逻辑电路图。

第4题

用VHDL描述下列器件的功能: (1)4选1数据选择器; (2)2线-4线译码器; (3)时钟R-S触

用VHDL描述下列器件的功能: (1)4选1数据选择器; (2)2线-4线译码器; (3)时钟R-S触发器; (4)带复位端Clear和置位端Preset、延迟Tpd为20ns的响应CP下降沿的J-K触发器; (5)主从J-K触发器; (6)集成计数器74163; (7)集成移位寄存器74194。

第8题

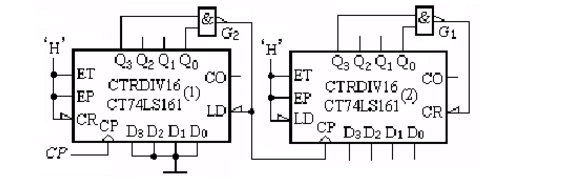

分析图中两片中规模同步计数器CT74LS161构成的计数分频器的模值。第(1)片CT74LS161为低位计数器,第(2)片CT74

分析图中两片中规模同步计数器CT74LS161构成的计数分频器的模值。第(1)片CT74LS161为低位计数器,第(2)片CT74LS161为高位计数器。并用两片同步十进制计数器集成芯片CT74LS160采用异步复位和级间同步连接法构成模值M=85的8421BCD计数器。

第9题

试用集成中规模异步二-五-十进制计数器CT74LS290设计一个输出为对称方波的十进制计数器。

试用集成中规模异步二-五-十进制计数器CT74LS290设计一个输出为对称方波的十进制计数器。

如果结果不匹配,请

如果结果不匹配,请