题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

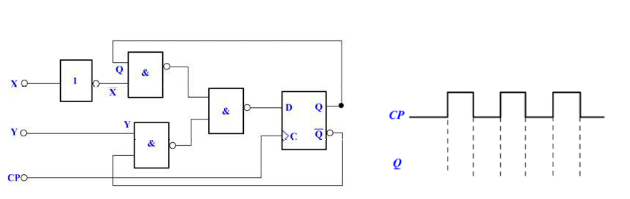

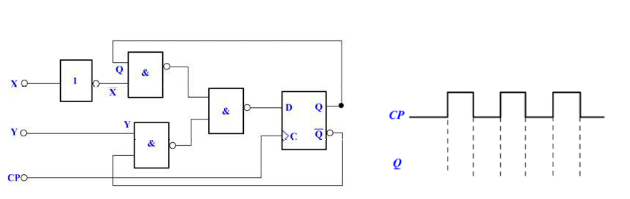

由D触发器和逻辑门构成的时序逻辑电路如图21-65所示,X,Y为输入端,CP为控制脉冲输入端,Q为输出端,(1)写出D的

由D触发器和逻辑门构成的时序逻辑电路如图21-65所示,X,Y为输入端,CP为控制脉冲输入端,Q为输出端,

(1)写出D的逻辑式。

(2)当输入端子保持在X=Y=0时,在图中画出输出端Q的波形图。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

由D触发器和逻辑门构成的时序逻辑电路如图21-65所示,X,Y为输入端,CP为控制脉冲输入端,Q为输出端,

(1)写出D的逻辑式。

(2)当输入端子保持在X=Y=0时,在图中画出输出端Q的波形图。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“由D触发器和逻辑门构成的时序逻辑电路如图21-65所示,X,…”相关的问题

更多“由D触发器和逻辑门构成的时序逻辑电路如图21-65所示,X,…”相关的问题

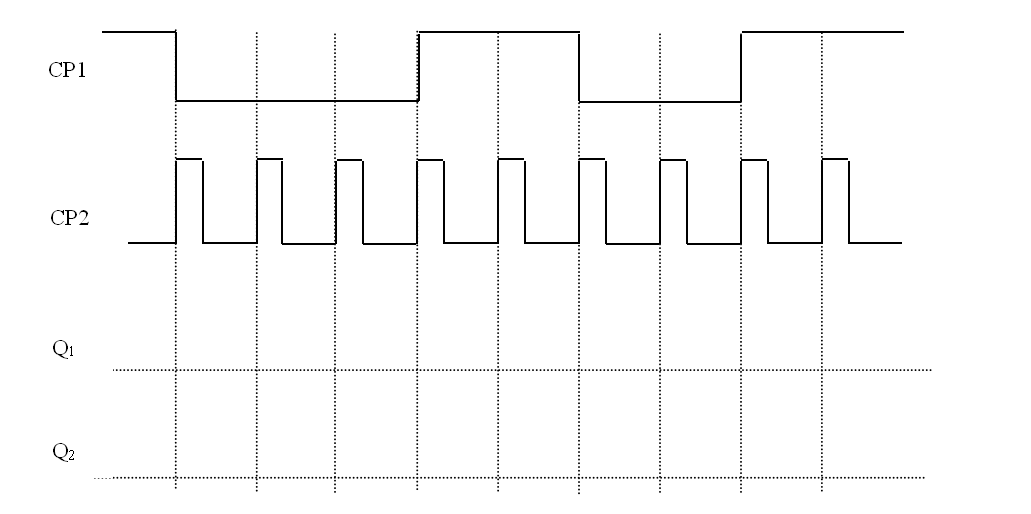

分析由JK触发器组成如图4.2.69所示的时序逻辑电路。分析电路的逻辑功能,画出Q1、Q2输出波形。设初始状态是11。

由JK触发器和PLA构成的时序逻辑电路如图所示,试分析其功能(写出驱动方程和状态方程,画出状态转换图,说明电路的逻辑功能,电路能否自启动)。

硬布线控制器是一种()。

A.用微程序技术设计的控制器

B.由门电路和触发器构成的复杂树形网络所形成的逻辑电路

C.用存储逻辑技术设计的控制器

D.用微程序技术和存储逻辑技术设计的控制器