更多“时序逻辑电路的电路状态是指()。”相关的问题

更多“时序逻辑电路的电路状态是指()。”相关的问题

第2题

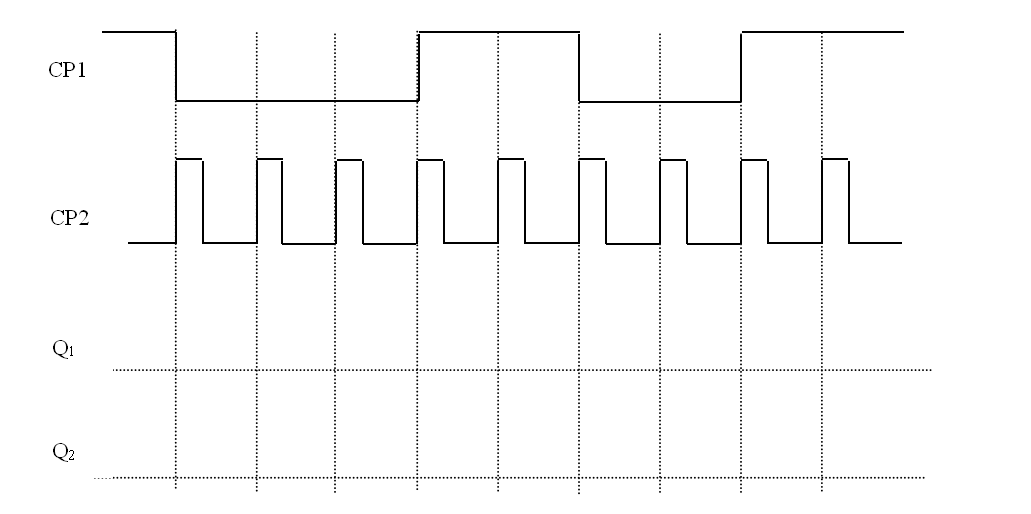

分析由JK触发器组成如图4.2.69所示的时序逻辑电路。分析电路的逻辑功能,画出Q1、Q2输出波形。设初始状态是11。

分析由JK触发器组成如图4.2.69所示的时序逻辑电路。分析电路的逻辑功能,画出Q1、Q2输出波形。设初始状态是11。

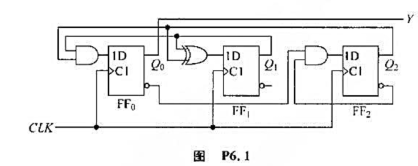

第4题

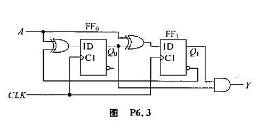

分析图6.7.1的时序逻辑电路,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自

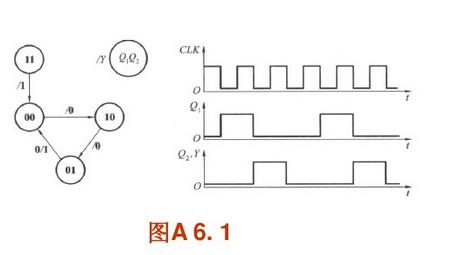

分析图6.1的时序逻辑电路,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。

第6题

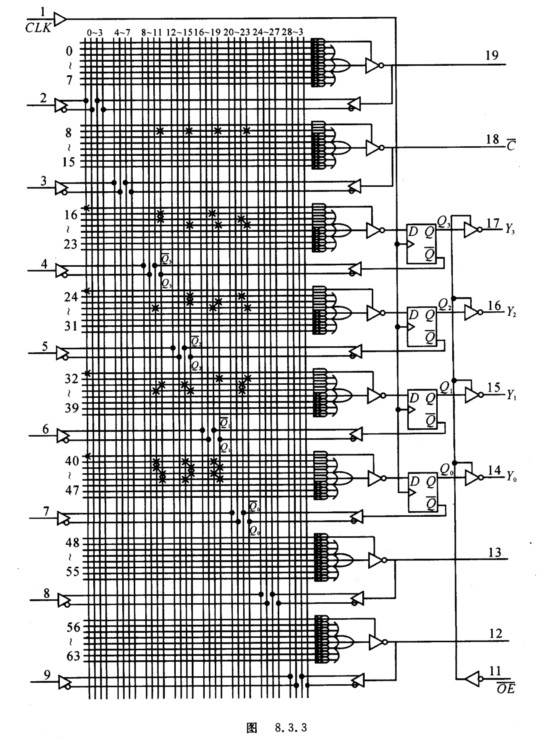

由JK触发器和PLA构成的时序逻辑电路如图所示,试分析其功能(写出驱动方程和状态方程,画出状态转换图,说明电

由JK触发器和PLA构成的时序逻辑电路如图所示,试分析其功能(写出驱动方程和状态方程,画出状态转换图,说明电路的逻辑功能,电路能否自启动)。

第9题

分析图所示的由中规模右移位寄存器74LS195和数据选择器74LS153组成的时序逻辑电路。画出状态转移图(以QA、QB、

分析图所示的由中规模右移位寄存器74LS195和数据选择器74LS153组成的时序逻辑电路。画出状态转移图(以QA、QB、QC、QD的顺序表示),分析电路的功能。74LS195已经处于移位的工作状态。

如果结果不匹配,请

如果结果不匹配,请