题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[单选题]

一个五位的二进制加法计数器,初始状态为00000,问经过201个输入脉冲后,此计数器的状态为______。

A.00111

B.00101

C.01000

D.01001

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.00111

B.00101

C.01000

D.01001

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“一个五位的二进制加法计数器,初始状态为00000,问经过20…”相关的问题

更多“一个五位的二进制加法计数器,初始状态为00000,问经过20…”相关的问题

A.250个

B.500个

C.750个

D.0111110100

E.111110100

集成计数器74LS161是()计数器。

A.四位二进制加法

B.四位二进制减法

C.五位二进制加法

D.三位二进制加法

A.100111

B.000100

C.111100

D.111101

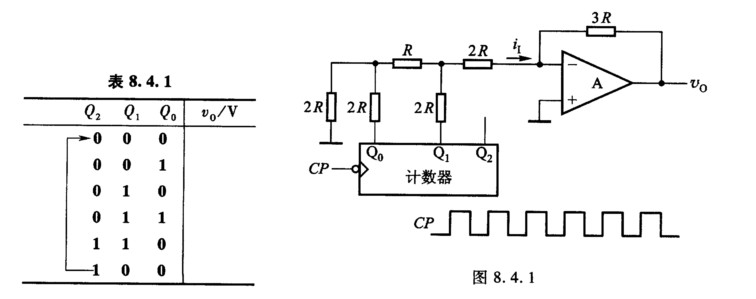

一个R-2R梯形网络D/A转换器如图8.4.1所示,图中计数器的初始状态Q2Q1Q=000,输出端高电平为8 V,低电平为0 V,计数器状态表如表8.4.1所示。将计数器各状态下D/A转换器的输出电压vO值填入表8.4.1中;并画出与CP对应的输出vO波形。

有效,使能端处于有效状态.

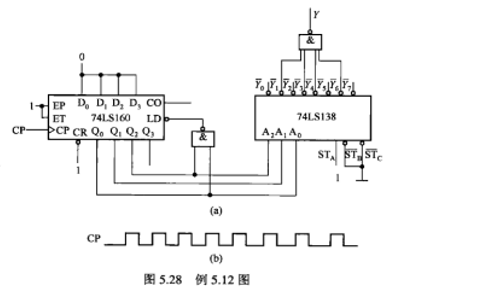

(1)74160构成多少进制计数器.

(2)假定74160初始状态Q3Q2Q1Q0=0000,试对应图5.28(b)的CP脉冲图画出Q3、Q2、Q1、Q0和Y的输出波形.