题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

基本的R-S触发器,禁止输入端R、S输入。()

A.R=1,S=1

B.R=0S=1

C.R=0S=0

D.R=1S=0

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.R=1,S=1

B.R=0S=1

C.R=0S=0

D.R=1S=0

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“基本的R-S触发器,禁止输入端R、S输入。()”相关的问题

更多“基本的R-S触发器,禁止输入端R、S输入。()”相关的问题

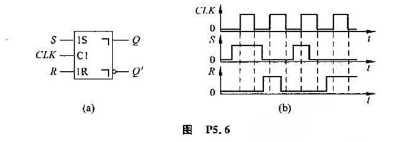

图P5.6(b)所示。设触发器的初始状态为Q=0。

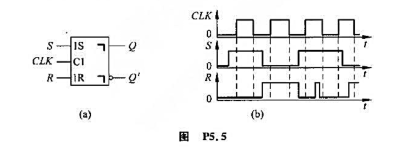

5.5(b)所示。设触发器的初始状态为Q=0。

基本RS触发器设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计基本RS触发器电路,建立基本RS触发器的实验模式。通过电路仿真和硬件验证,进一步了解基本RS触发器的功能和特性。

设计原理

基本RS触发器可以由两个与非门或者两个或非门构成。由两个与非门构成的基本RS触发器的原理图如图所示,其中RDN是异步置0输入端,低电平有效;SDN是异步置1输入端,低电平有效;Q是触发器的输出端,QN是反相输出端。由图所示的电路可知,基本RS触发器的输出表达式为

某单稳态触发器由555定时器组成,若其定时电容C=0.1μF,定时电阻R=10kΩ,输入信号脉冲宽度Tw=50μS,周期T=1500μs的负脉冲,则单稳的宽度为______μS,输出信号的周期为______μs。

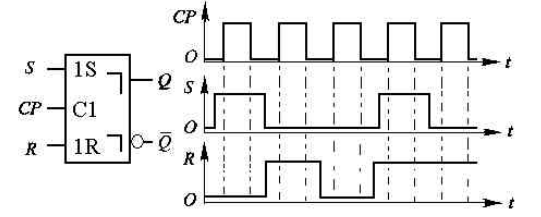

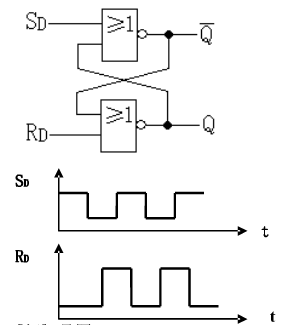

在图所示的由与非门组成的基本RS触发器中,加入图示的S和R波形,画出触发器Q和

A.J-K触发器

B.R-S基本触发器

C.D型触发器

D.R-S同步触发器

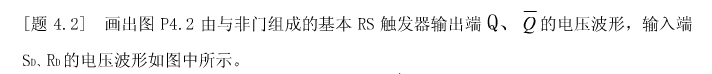

画出由与非门构成的基本RS触发器输出端Q和的电压波形,输入端和的电压波形分别如图题4.1(a)、(b)所示。

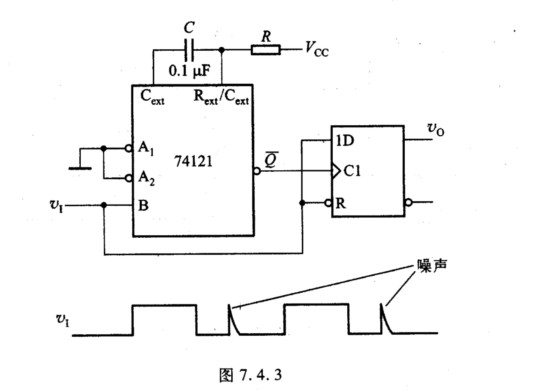

由单稳态触发器741 21构成的噪声消除电路及输入波形如图7.4.3所示。

(1)试说明消除噪声的原理,画出

(1)试说明消除噪声的原理,画出

及vO的波形; (2)若输入信号高电平持续时间为100μs,噪声宽度5μs,确定R的取值范围。

及vO的波形; (2)若输入信号高电平持续时间为100μs,噪声宽度5μs,确定R的取值范围。

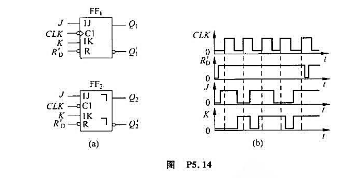

异步置零端R´D和输入端J、K的电压波形如图P5.14(b)所示。设触发器的初始状态均为Q=0。

将下图所示的输入波形加在由两个或非门组成的基本RS触发器上,试画出输出Q和 端的波形(设初始状态为Q=0) 。

端的波形(设初始状态为Q=0) 。