题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

用1片中规模移位寄存器74LS195和1片8选1数据选择器,设计1个移存型计数器,要求状态转移规律为1→2→4→9→3→6→12

→8→1→2→…设计时要求自启动,画出逻辑图。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

→8→1→2→…设计时要求自启动,画出逻辑图。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“用1片中规模移位寄存器74LS195和1片8选1数据选择器,…”相关的问题

更多“用1片中规模移位寄存器74LS195和1片8选1数据选择器,…”相关的问题

分析图所示的由中规模右移位寄存器74LS195和数据选择器74LS153组成的时序逻辑电路。画出状态转移图(以QA、QB、QC、QD的顺序表示),分析电路的功能。74LS195已经处于移位的工作状态。

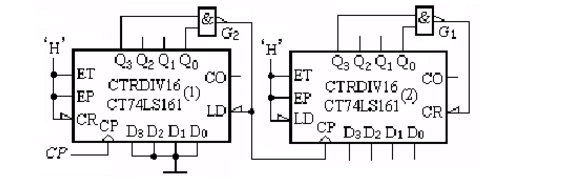

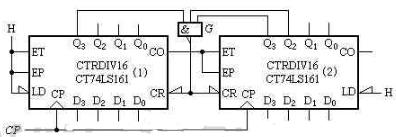

分析图中两片中规模同步计数器CT74LS161构成的计数分频器的模值。第(1)片CT74LS161为低位计数器,第(2)片CT74LS161为高位计数器。并用两片同步十进制计数器集成芯片CT74LS160采用异步复位和级间同步连接法构成模值M=85的8421BCD计数器。

分析图所示的由两片中规模同步计数器CT74LS161构成的计数分频器的模值。第(1)片CT74LS161为低位计数器,第(2)片CT74LS161为高位计数器。

用VHDL描述下列器件的功能: (1)4选1数据选择器; (2)2线-4线译码器; (3)时钟R-S触发器; (4)带复位端Clear和置位端Preset、延迟Tpd为20ns的响应CP下降沿的J-K触发器; (5)主从J-K触发器; (6)集成计数器74163; (7)集成移位寄存器74194。

试用J-K触发器构成一个三位移位寄存器,它在两个控制信号x1和x2的作用下实现表5-24所示的功能。

表5-24 功能表 | ||

x1 | x2 | 功能 |

0 | 0 | 保持 |

0 | 1 | 右移 |

1 | 0 | 左移 |

1 | 1 | 置零 |

A.PN序列是随机的,他们是非确定的、非周期性的序列

B.0和1出现的相对概率各为1/2

C.如果一个PN序列被任意的非零元素移位,得到的序列与原始序列相比,一致的位数和不一致的位数是相等的

D.PN序列通过组合反馈移位寄存器的输出组成

A.其值代表多少输出变异总量可由回归模型所解释

B.其值介于-1到+1之间

C.值越小表示该模型的可信度越高

D.与相关系数毫无关系

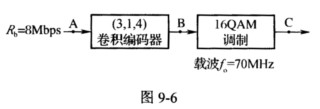

取值1、0的二进制独立等概序列经(3,1,4)卷积编码(卷积编码器的约束长度K=4,移位寄存器级数为m=K-4=3)后,送至16QAM数字调制器,如图9-6所示。已知此卷积码的生成多项式是g1(x)=1,g2(x)=l+x2+x3, g3(x)=l+x+x2+x3。 (1)画出卷积码编码器电路; (2)求出图9-6中B、C处的码元速率,画出C点的功率谱密度图;

(3)画出16QAM的信号空间图,并求出星座图中最小的欧式距离平方和平均能量之比(假设采用常规矩形星座,各星座点等概出现)。

(3)画出16QAM的信号空间图,并求出星座图中最小的欧式距离平方和平均能量之比(假设采用常规矩形星座,各星座点等概出现)。

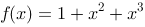

设一个3级线性反馈移位寄存器(LFSR)的特征多项式为 。 (1) 画出该LFSR的框图; (2) 给出输出序列的递推关系式; (3) 设初始状态(a0,a1,a2)=(0,0,1),写出输出序列及序列周期。 (4) 列出序列的游程。

。 (1) 画出该LFSR的框图; (2) 给出输出序列的递推关系式; (3) 设初始状态(a0,a1,a2)=(0,0,1),写出输出序列及序列周期。 (4) 列出序列的游程。