更多“TTL、CMOS门中未使用的输入端均可悬空()”相关的问题

更多“TTL、CMOS门中未使用的输入端均可悬空()”相关的问题

A.电源电压极性不得接反,其额定值为5V

B.与非门不使用的输入端接“1”

C.与非门输入端可以串有电阻器,但其值不应大于该门电阻

D.三态门的输出端可以并接,但三态门的控制端所加的控制信号电平只能使其中一个门处于工作状态,而其它所有相并联的三态门均处于高阻状态

E.或非门不使用的输入端接“0”

A.电源电压极性不得接反,其额定值为5V

B.与非门不使用的输入端接“1”

C.与非门输入端可以串有电阻器,但其值不应大于该门电阻

D.三态门的输出端可以并接,但三态门的控制端所加的控制信号电平只能使其中一个门处于工作状态,而其它所有相并联的三态门均处于高阻状态

E.或非门不使用的输入端接“0”

A.将多余端与使用端连接在一起

B.将多余端悬窄

C.将多余端通过一个电阻接工作电源

D.将多余端接地

E.将多余端直接接电源

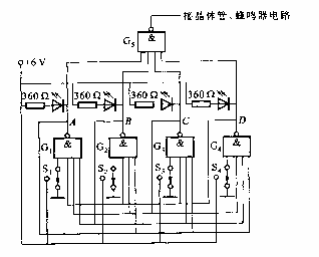

题图所示是一智力竞赛抢答电路,供四组使用。每一组由TTL四输入“与非”门、指示灯(发光二极管)、抢答开关S组成。“与非”门G5以及由其输出端接出的晶体管电路和蜂鸣器电路是共用的,当G5输出高电平时,蜂鸣器响。(1) 当抢答开关如图示位置,指示灯能否发亮?蜂鸣器能否响?(2) 分析A组扳动抢答开关S1(由接“地”点扳到+6V)时的情况,此后其他组再扳动各自的抢答开关是否起作用。(3) 试画出接在G5输出端的晶体管电路和蜂鸣器电路。

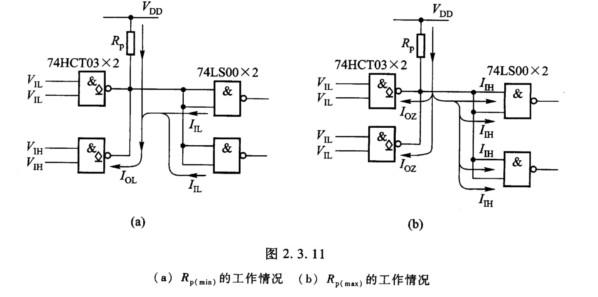

图P3.6是用输出端并联的OD门驱动CMOS反相器和与非门的电路。试计算当VDD=5V时外接电阻RP阻值的合理范围。要求OD门输出的高、低电平满足VOH≥3.5V、VOL≤0.3V。已知OD门G1~G3输出高电平时,每个输出端MOS管的漏电流为IOH(max)=10μA;输出低电平时,每个输出端MOS管输出电流的最大值为IOL(max)=4mA,输出低电平VOL≤0.3V。CMOS反相器和与非门每个输入端的高电平输入电流和低电平输入电流最大值均为1μA。

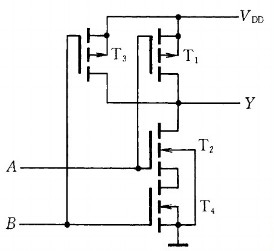

TTL门驱动CMOS门时,如果不满足VOH(min)≥VIH(min),常用的解决方法是____________。

如果结果不匹配,请

如果结果不匹配,请