更多“与4位串行进位加法器比较,使用超前进位全加器目的是提高运算的…”相关的问题

更多“与4位串行进位加法器比较,使用超前进位全加器目的是提高运算的…”相关的问题

第1题

串行进位加法器的缺点是_______________ ,优点是 _______________ 。超前进位加法器的优点是 ___

____________ ,缺点是 _______________。

点击查看答案

第2题

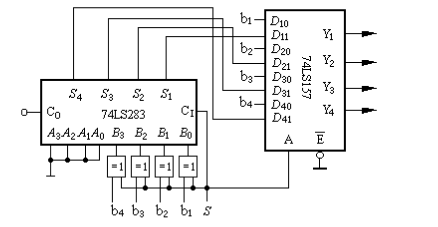

由4位超前进位加法器74LS283和4位2选1数据选择器74LS157组成的电路如下图所示,其中S为输入控制信号。试填写

下表所示的输入/输出对照表。

| 输入/输出对照表 | |||||||||||

| 输入 | S=0 | S=1 | |||||||||

| b4 | b3 | b2 | b1 | Y4 | Y3 | Y2 | Y1 | Y4 | Y3 | Y2 | Y1 |

| 0 | 0 | 0 | 0 | ||||||||

| 0 | 0 | 1 | 1 | ||||||||

| 0 | 1 | 0 | 1 | ||||||||

| 0 | 1 | 1 | 0 | ||||||||

| 1 | 0 | 0 | 1 | ||||||||

| 1 | 0 | 1 | 0 | ||||||||

| 1 | 1 | 0 | 0 | ||||||||

| 1 | 1 | 1 | 1 |

第4题

在串行进位的并行加法器中,影响加法器运算速度的关键因素是()。A.门电路的级延迟B.元器件速

在串行进位的并行加法器中,影响加法器运算速度的关键因素是()。

A.门电路的级延迟

B.元器件速度

C.进位传递延迟

D.各位加法器速度的不同

第9题

试用一片超前进位4位全加器CC4008,将4位二进制码转换成8421BCD码。 提示 在输入代码为0000~1001时,二码相同

试用一片超前进位4位全加器CC4008,将4位二进制码转换成8421BCD码。

提示 在输入代码为0000~1001时,二码相同;当输入二进制码为1010~1111时须变为2位BCD码,逢十进1,即“1010(2)”变为“10000(BCD)”、“1011(2)”变为“10001(BCD)”……“1111(2)”变为“10101(BCD)”,如果把后者也看成二进制码,则与转换前恒差6。

第10题

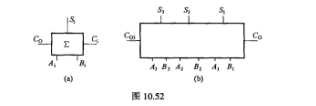

已知一位二进制全加器逻辑符号如图10.52(a)所示,进位输出表达式Co=G+P·Ci(其中G=Ai⌘

已知一位二进制全加器逻辑符号如图10.52(a)所示,进位输出表达式Co=G+P·Ci(其中G=Ai⌘

点击查看答案

已知一位二进制全加器逻辑符号如图10.52(a)所示,进位输出表达式Co=G+P·Ci(其

中G=Ai·Bi,P=Ai+Bi),试求采用超前进位结构的三位二进制加法器(如图10.52(b)所示)的最高位进位输出表达式Co3.

如果结果不匹配,请

如果结果不匹配,请