题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

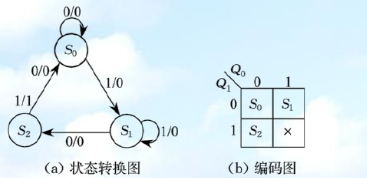

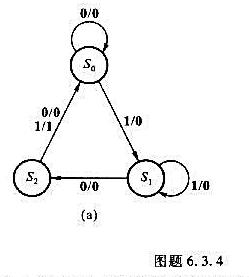

试用上升沿触发的JK触发器设计一同步时序电路,其状态图如下图所示,要求电路使用的门电路最少。

答案

答案

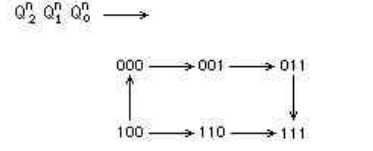

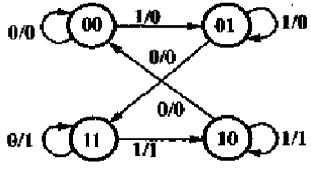

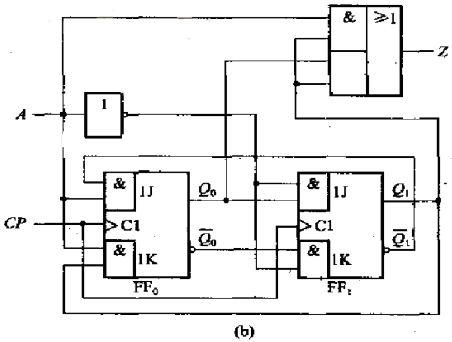

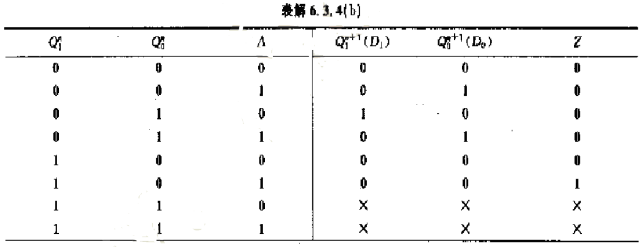

由图题知电路共有4个状态,因此可用2个上升沿触发的JK触发器来实现,其输出分别为Q1、Q0,作出对应的状态表如下表所示。依据JK触发器的激励表即下列第一个表及第二个表,列出状态转换真值表及两个触发器所要求的激励信号,如最后一个表所示。

| Q_{1}^{n}Q_{0}^{n} | Q_{1}^{n+1}Q_{0}^{n+1} | |

| A=0 | A=1 | |

| 0 0 0 1 1 0 1 1 | 0 0/0 1 1/0 0 0/0 1 1/1 | 0 1/0 0 1/0 1 0/1 1 0/1 |

| AQ_{1}^{n}Q_{0}^{n} | Q_{1}^{n+1}Q_{0}^{n+1} | Z | J_{1}K_{1} | J_{0}K_{0} |

| 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 | 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 | 0 0 0 1 0 0 1 1 | 0 × 1 × × 1 × 0 0 × 0 × × 0 × 0 | 0 × × O 0 × × 0 1 × × 0 0 × × 1 |

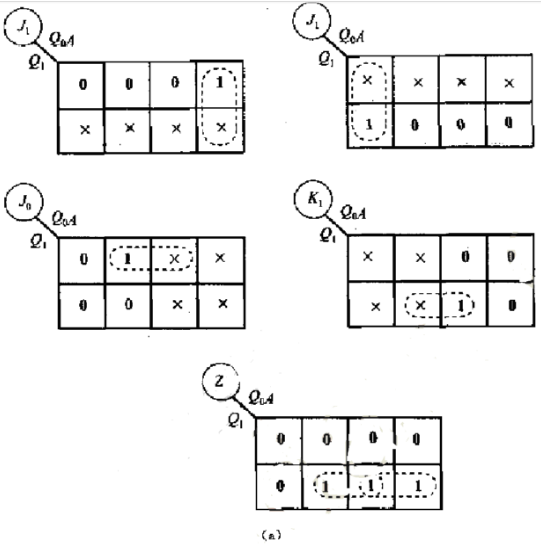

再由真值表分别画出各触发器激励信号及输出信号的卡诺图,如下图(a)所示。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“试用上升沿触发的JK触发器设计一同步时序电路,其状态图如下图…”相关的问题

更多“试用上升沿触发的JK触发器设计一同步时序电路,其状态图如下图…”相关的问题