题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

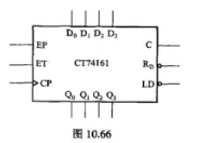

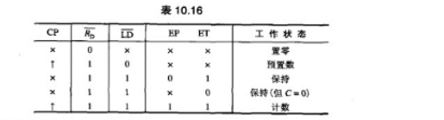

图11-20是一个四位右移寄存器,其输入信号波形和时钟脉冲波形如图11-30(a)所示,试根据输入信号波形和时钟脉

图11-20是一个四位右移寄存器,其输入信号波形和时钟脉冲波形如图11-30(a)所示,试根据输入信号波形和时钟脉冲波形画出移位寄存器的各位输出端的波形图。设移位寄存器的初始状态Q3、Q2、Q1、Q0均为“0”。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图11-20是一个四位右移寄存器,其输入信号波形和时钟脉冲波形如图11-30(a)所示,试根据输入信号波形和时钟脉冲波形画出移位寄存器的各位输出端的波形图。设移位寄存器的初始状态Q3、Q2、Q1、Q0均为“0”。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“图11-20是一个四位右移寄存器,其输入信号波形和时钟脉冲波…”相关的问题

更多“图11-20是一个四位右移寄存器,其输入信号波形和时钟脉冲波…”相关的问题

图13.13所示电路是右移寄存器还是左移寄存器?设待存数码为1001,画出Q4,Q3,Q2,Q1的波形,列出状态表。

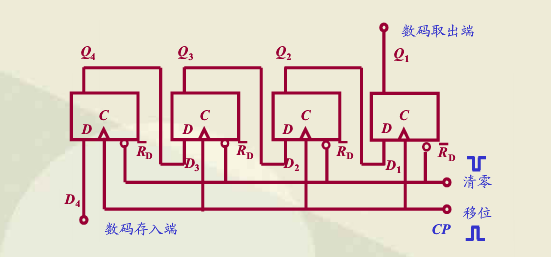

(1)试在三个寄存器中用英文符号标其名称,其中a为________,b为________,c为________。 (2)同时具有左移、右移功能的寄存器为________。 (3)用规定的英文符号写出加、减、乘、除四种运算中三个寄存器的配置及操作表达式,加法:________,减法:________,乘法:________,除法:________。

(1)试在三个寄存器中用英文符号标其名称,其中a为________,b为________,c为________。 (2)同时具有左移、右移功能的寄存器为________。 (3)用规定的英文符号写出加、减、乘、除四种运算中三个寄存器的配置及操作表达式,加法:________,减法:________,乘法:________,除法:________。

A、1011--0110--1100--1000--0000

B、1011--0101--0010--0001--0000

C、1011--1100--1101--1110--1111

D、1011--1010--1001--1000--0111