题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

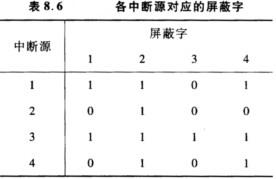

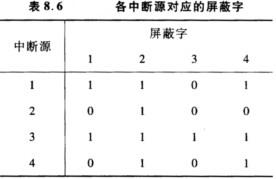

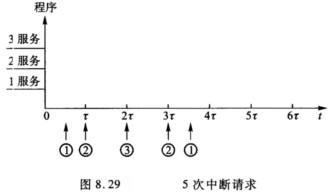

设某机有四个中断源1、2、3、4,其硬件排队优先次序按1→2→3→4降序排列,各中断源的服务程序中所对应的

(1)给出上述四个中断源的中断处理次序。 (2)若四个中断源同时有中断请求,画出CPU执行程序的轨迹。

(1)给出上述四个中断源的中断处理次序。 (2)若四个中断源同时有中断请求,画出CPU执行程序的轨迹。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

(1)给出上述四个中断源的中断处理次序。 (2)若四个中断源同时有中断请求,画出CPU执行程序的轨迹。

(1)给出上述四个中断源的中断处理次序。 (2)若四个中断源同时有中断请求,画出CPU执行程序的轨迹。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“设某机有四个中断源1、2、3、4,其硬件排队优先次序按1→2…”相关的问题

更多“设某机有四个中断源1、2、3、4,其硬件排队优先次序按1→2…”相关的问题

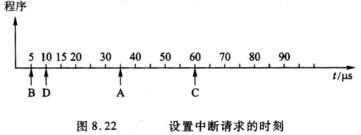

设某机有六个中断源,优先顺序按0→1→2→3→4→5降序排列。 (1)若在某用户程序的运行过程中,依次发生了3、2、1级中断请求,画出CPU的程序运行轨迹。 (2)若在3、2、1级中断请求发生之前,用改变屏蔽字的方法,将优先级的顺序从高到低改为0→5→3→4→1→2。试在与(1)相同的请求顺序和请求时间的情况下,画出CPU程序的运行轨迹。

有4个中断源D1、D2、D3和D4,它们的中断优先级从高到低分别是1级、2级、3级和4级。即中断响应先后次序为1→2→3→4,现要求其实际的中断处理次序为4→3→2→1。

(1)写出这些中断源的正常中断屏蔽码和改变后的中断屏蔽码(令“0”对应于开放,“1”对应于屏蔽)。

(2)若在运行用户程序时,同时出现第1、2、3、4级中断请求,请画出此程序运行过程示意图。

A.3→2→1→4

B.1→3→4→2

C.2→1→3→4

(1)画出硬件连接图

(2)编写全部初始化程序

设某机共能完成120种操作,CPU有8个通用寄存器(12位),主存容量为16K字,采用寄存器—存储器型指令。 (1)欲使指令可直接访问主存的任一地址,指令字长应取多少位? (2)若在上述设计的指令字中设置一寻址特征位X,且X=0表示某个寄存器作基址寄存器,画出指令格式。试问采用基址寻址可否访问主存的任一单元?为什么?如不能,提出一种方案,使指令可访问主存的任一位置。 (3)若指令字长等于存储字长,且主存容量扩大到64K字,在不改变硬件结构的前提下,可采用什么方法使指令可访问存储器的任一位置?

A.有四个实根,分别为1、2、3、4

B.有三个实根,分别位于(1,2),(2,3)和(3,4)之内

C.有两个实根,分别位于(2,3),(3,4)之内

D.有一个实根,位于(2,3)之内