题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

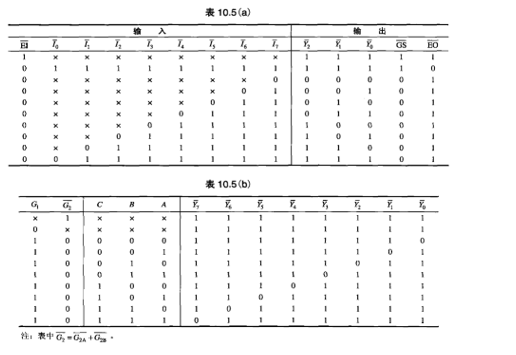

已知程序表10.5,分别写出组合逻辑控制部件和微程序控制部件所发出的全部微命令及节拍安排(指令地

已知程序表10.5,分别写出组合逻辑控制部件和微程序控制部件所发出的全部微命令及节拍安排(指令地址和操作数地址均用十六进制数表示)。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

已知程序表10.5,分别写出组合逻辑控制部件和微程序控制部件所发出的全部微命令及节拍安排(指令地址和操作数地址均用十六进制数表示)。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“已知程序表10.5,分别写出组合逻辑控制部件和微程序控制部件…”相关的问题

更多“已知程序表10.5,分别写出组合逻辑控制部件和微程序控制部件…”相关的问题

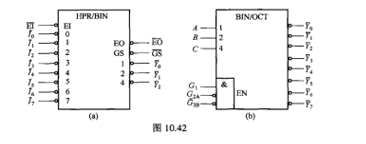

.42(b)和表10.5(b)所示.试用1片二进制优先编码器74148、1片二进制译码器74138和少量与门设计一个8-3格雷码编码器.要求写出设计过程,画出电路图(3位二进制码A2A1A0和对应格雷码B2B1B0之间的关系为B2=A2其他 ).

).

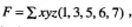

已知逻辑关系表达式为 ,写出该逻辑的最小式和表达式、最小积表达式、并分别画出对应的逻辑电路图.

,写出该逻辑的最小式和表达式、最小积表达式、并分别画出对应的逻辑电路图.

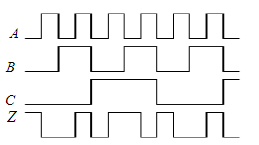

已知图3.2.103所示组合逻辑电路的输入和输出波形,试用一片4选1数据选择器实现此电路。要求:(1)写出输出函数Z的逻辑表达式:(2)画出逻辑线路图。

高电平为读,低电平为写)。

已知该机存储器地址空间从0连续编址,其地址空间分配如下:最低8K为系统程序区,由ROM芯片组成;紧接着40K为备用区,暂不连接芯片;而后78K为用户程序和数据空间,用静态RAM芯片组成;最后2K用于I/O设备(与主存统一编址)。现有芯片如下:

SRAM:16K×8位,其中CS:为片选信号,低电平有效,WE:为写控制信号,低电平写,高电平读。

ROM:8K×8位,其中CS:为片选信号,低电平有效,OE:为读出控制,低电平读出有效。

译码器:3―8译码器,输出低电平有效;为使能信号,低电平时译码器功能有效。

其它“与、或”等逻辑门电路自选。

(1)请问该主存需多少SRAM芯片?

(2)试画出主存芯片与CPU的连接逻辑图。

(3)写出各芯片地址分配表。

设CPU内部结构如图10.11所示,且PC有自动加1功能。此外还有B、C、D、E、H、L六个寄存器(图中未画),它们各自的输入端和输出端都与内部总线Bus相连,并分别受控制信号控制。要求写出完成下列指令组合逻辑控制单元所发出的微操作命令及节拍安排。 (1)ADD B,C ;(B)+(C)→B (2)SUB E,@H ;(E)-((H))→E 寄存器间接寻址 (3)STA @mem ;ACC→((mem)) 存储器间接寻址

安装在9m处。当水面低于检测头时对应的逻辑电平为0,高于检测头时逻辑电平为1。试用与非门设计一个组合逻辑电路,水箱中的水面高度用一个七段显示数码管来显示。要求只写出逻辑表达式,数码管如图3.2.15所示。

已知运输问题的产销平衡表、单位运价表及最优调运方案,试回答下列问题。

(1)从A2→B2的单位运价c22在什么范围变化时,上述最优调运方案不变?

(2)A2→B4的单位运价c24变为何值时,有无穷多最优调运方案。除表3-32中方案外,至少再写出其他两个。