更多“用PROM实现一位全加器,画出阵列图。”相关的问题

更多“用PROM实现一位全加器,画出阵列图。”相关的问题

第1题

画出实现n位小数(不包括符号位在内)的补码一位乘运算器框图。要求: (1)指出寄存器和全加器位

画出实现n位小数(不包括符号位在内)的补码一位乘运算器框图。要求: (1)指出寄存器和全加器位数; (2)详细画出最低位全加器的输入电路; (3)描述重复加和移位的操作; (4)指出加和移位次数。

第2题

设机器数字长为n位(不包括符号位),画出补码一位乘的运算器框图(图中必须反映补码一位乘算法),要

设机器数字长为n位(不包括符号位),画出补码一位乘的运算器框图(图中必须反映补码一位乘算法),要求: (1)寄存器和全加器均用方框表示; (2)指出每个寄存器的位数及寄存器中操作数的名称; (3)详细画出第5位全加器的输入逻辑电路; (4)描述补码一位乘法过程中的重复加和移位操作。

第3题

设机器数字长为n位(不包括符号位),画出原码一位乘的运算器框图(图中必须反映原码一位乘算法),要

设机器数字长为n位(不包括符号位),画出原码一位乘的运算器框图(图中必须反映原码一位乘算法),要求: (1)寄存器和全加器均用方框表示; (2)指出每个寄存器的位数及寄存器中操作数的名称; (3)详细画出第5位全加器的输入逻辑电路(设第n位为最低位); (4)描述原码一位乘法过程中的重复加和移位操作。

第4题

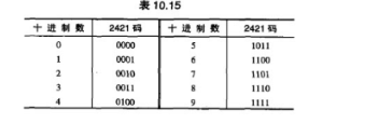

图10.64为4位二进制全加器CT74283的逻辑符号.试用此器件及尽可能少的与非门设计一个代码转换电

路,实现BCD代码的8421码到2421码的转换,2421码如表10.15所示.

点击查看答案

要求写出设计过程,并画出连接图.

第5题

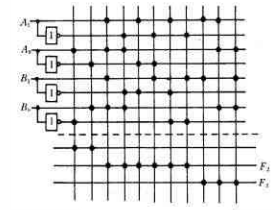

16×4位EPROM有四个地址输入端和四个数据输出端,可以实现四输入变量、四输出变量的逻辑函数,画出阵列图。 Y1=

16×4位EPROM有四个地址输入端和四个数据输出端,可以实现四输入变量、四输出变量的逻辑函数,画出阵列图。

第6题

用CPLD中的查找表LUT(L00k up Table)结构实现: (1)一位全加器; (2)余3 BCD码计数器。

用CPLD中的查找表LUT(L00k up Table)结构实现: (1)一位全加器; (2)余3 BCD码计数器。

第8题

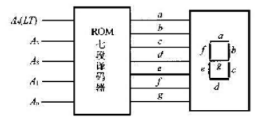

图22.17是用ROM构成的七段译码电路框图。A4~A0为ROM的输入端。A3~A0是数据输入端,最高位A4只用作试灯输入端(L

图22.17是用ROM构成的七段译码电路框图。A4~A0为ROM的输入端。A3~A0是数据输入端,最高位A4只用作试灯输入端(LT)。当LT=1时,不论二进制数码A3A2A1A0为何值,数码管七段全亮。当LT=0时,数码管则显示四位二进制数所对应的十进制数码。半导体数码管为共阴极接法。试列出实现上述逻辑要求的ROM功能表,并画出ROM的阵列图。

第10题

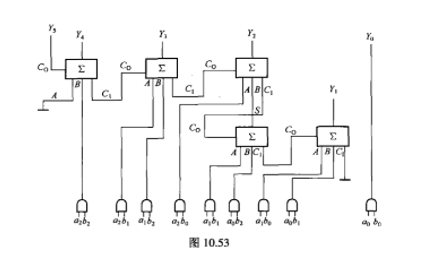

分析图10.53所示逻辑电路,图中∑为一位全加器.试求:(1)当a2a1a0=(110)Bb2b

分析图10.53所示逻辑电路,图中∑为一位全加器.试求:(1)当a2a1a0=(110)Bb2b

点击查看答案

1b0=(111)B时,Y5Y4Y3Y2Y1=()B(2)简要描述该电路的逻辑功能.

如果结果不匹配,请

如果结果不匹配,请