题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

已知某64位机主存采用半导体存储器,其地址码为26位,若使用4M×8位的DRAM芯片组成该机所允许的最大主存空间,并选用内存条结构形式,问: (1)每个内存条内共有多少DRAM芯片? (2)主存共需多少DRAM芯片?

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“已知某64位机主存采用半导体存储器,其地址码为26位,若使用…”相关的问题

更多“已知某64位机主存采用半导体存储器,其地址码为26位,若使用…”相关的问题

A.半导体材料做的内存;内存

B.高速缓冲;主存

C.内部;辅助存储器

D.外部;硬盘

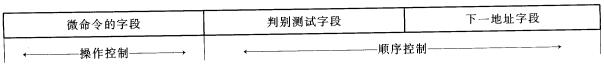

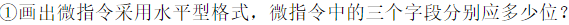

则微指令中3个字段分别应为多少位?

则微指令中3个字段分别应为多少位?

设某机共能完成120种操作,CPU有8个通用寄存器(12位),主存容量为16K字,采用寄存器—存储器型指令。 (1)欲使指令可直接访问主存的任一地址,指令字长应取多少位? (2)若在上述设计的指令字中设置一寻址特征位X,且X=0表示某个寄存器作基址寄存器,画出指令格式。试问采用基址寻址可否访问主存的任一单元?为什么?如不能,提出一种方案,使指令可访问主存的任一位置。 (3)若指令字长等于存储字长,且主存容量扩大到64K字,在不改变硬件结构的前提下,可采用什么方法使指令可访问存储器的任一位置?

某计算机的主存采用体宽为8B的8体交叉存储器,数据总线的宽度为64位,读一个主存块的步骤: (1)发送首地址到主存(一个总线时钟周期); (2)主存控制器接受到地址后,启动第一个模块准备数据,并每隔一个总线时钟启动下一个模块准备数据。每个存储模块花4个总线时钟准备好64位数据,总线上传输一个64位数据花一个总线时钟。请问: 该计算机的Cache缺失损失(从主存中读一个主存块到Cache的时间)至少为多少总线时钟周期?

微程序转移的条件共4个,微指令采用水平型格式,后继微指令地址采用断定方式,如下所示。

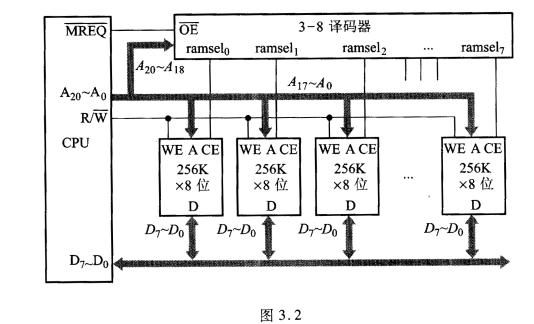

某计算机的主存地址空间中,从地址0000H~3FFFH为ROM存储区域,从地址

4000H~7FFFH为RAM的存储区域。RAM的控制信号为CS和WE,CPU的地址线为A15~A0,数据线为8位的D7~D0线,控制信号有读写控制R/W和访存请求MREQ,要求: (1)画出地址译码方案。 (2)如果ROM和RAM存储器芯片都采用8 K×1位的芯片,试画出存储器与CPU的连接图。 (3)如果ROM存储器芯片采用8K×8位的芯片,RAM存储器芯片采用4K×8位的芯片, 试画出存储器与CPU的连接图。 (4)如果ROM存储器芯片采用16K×8位的芯片,RAM存储器芯片采用8K×8位的芯片,试画出存储器与CPU的连接图。

4000H~7FFFH为RAM的存储区域。RAM的控制信号为CS和WE,CPU的地址线为A15~A0,数据线为8位的D7~D0线,控制信号有读写控制R/W和访存请求MREQ,要求: (1)画出地址译码方案。 (2)如果ROM和RAM存储器芯片都采用8 K×1位的芯片,试画出存储器与CPU的连接图。 (3)如果ROM存储器芯片采用8K×8位的芯片,RAM存储器芯片采用4K×8位的芯片, 试画出存储器与CPU的连接图。 (4)如果ROM存储器芯片采用16K×8位的芯片,RAM存储器芯片采用8K×8位的芯片,试画出存储器与CPU的连接图。