更多“试画出用3线—8线译码器74LS138和门电路产生如下多输出…”相关的问题

更多“试画出用3线—8线译码器74LS138和门电路产生如下多输出…”相关的问题

第1题

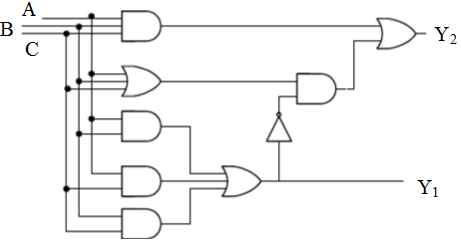

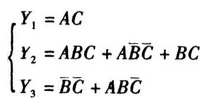

用3线—8线译码器设计一个既能做一位二进制数的令加运算,又能做一位二进制数的伞减运算的电路。 要求:(1)根

用3线—8线译码器设计一个既能做一位二进制数的令加运算,又能做一位二进制数的伞减运算的电路。

要求:(1)根据题意要求,写真值表。

(2)写出电路输出函数的最简与或表达式。

(3)画出用3线—8线译码器74LS138芯片实现的电路。

第4题

TTL集成电路74LS138是3/8线译码器,译码器是输出低电平有效,若输入为A2A1A0=101时,输出Y7-Y0为()。

A.00100000

B.11011111

C.11110111

D.00000100

第6题

由移位寄存器74HCl94和3线-8线译码器74HCl38组成的电路如图5.3.27所示,分析电路,列出状态表,并画

由移位寄存器74HCl94和3线-8线译码器74HCl38组成的电路如图5.3.27所示,分析电路,列出状态表,并画出输出端L的波形。

1.jpg)

第8题

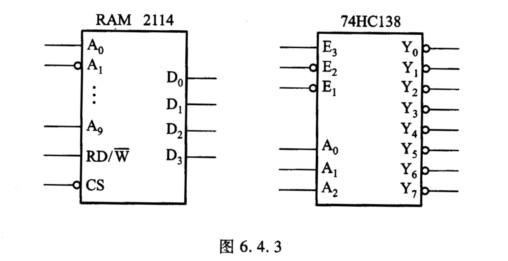

RAM 2114芯片(容量为1 K×4位)和3线-8线译码器74HCl38的简化框图如图6.4.3所示,试用这两种类型的

RAM 2114芯片(容量为1 K×4位)和3线-8线译码器74HCl38的简化框图如图6.4.3所示,试用这两种类型的芯片组成4 K×8位的存储器系统,写出设计思想,画出逻辑图。

第9题

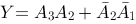

试画出用4片8线-3线优先编码器74HC148组成32线-5线优先编码器的逻辑图。74HC148的逻辑图见图4.8.1。允许附加

试画出用4片8线-3线优先编码器74HC148组成32线-5线优先编码器的逻辑图。74HC148的逻辑图见图4.8.1。允许附加必要的门电路。

第10题

用3—8译码器(74LS138)和必要的逻辑门实现下面两个逻辑函数,要求画在一个逻辑电路中。 F1(A,B,C)= F2(A,B,C

用3—8译码器(74LS138)和必要的逻辑门实现下面两个逻辑函数,要求画在一个逻辑电路中。

F1(A,B,C)=

F2(A,B,C)=

如果结果不匹配,请

如果结果不匹配,请

,应该()。

,应该()。