题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

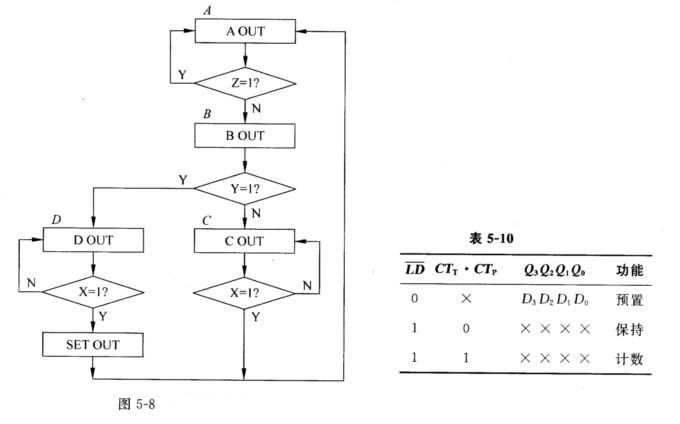

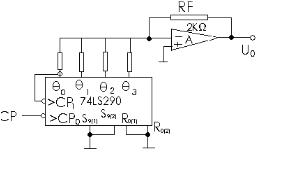

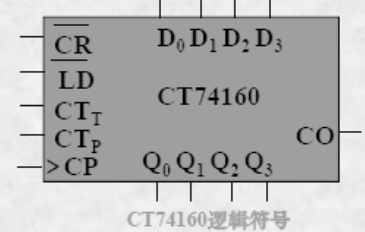

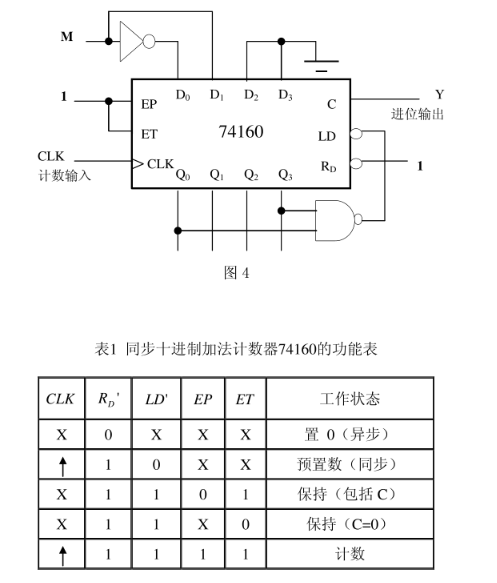

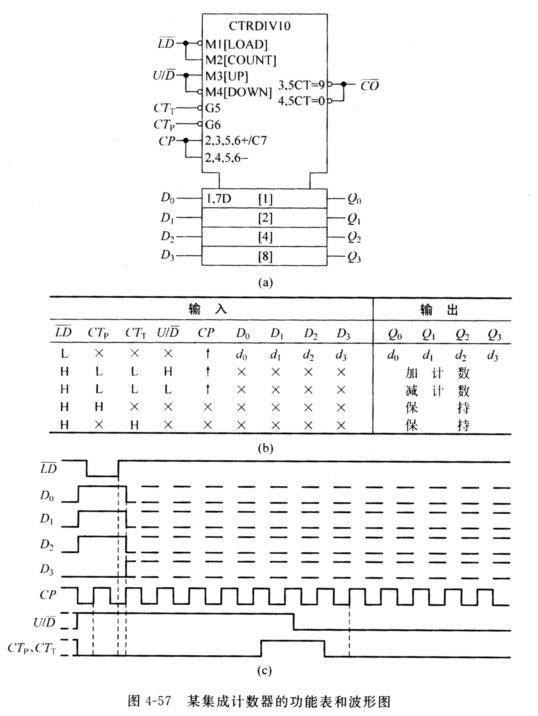

74LS290集成计数器的功能如表所示,其简化符号如图9所示。要求: R0(1) R0(2) S9(1) S9(2) Q3n+1Q

74LS290集成计数器的功能如表所示,其简化符号如图9所示。要求:

| R0(1)R0(2)S9(1)S9(2) | Q3n+1Q2n+1Q1n+1Q0n+1 |

| 110× 11×0 ××11 | 0000 0000 1001 |

| ×0×0 0×0× 0××0 ×00× | 计数 |

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“74LS290集成计数器的功能如表所示,其简化符号如图9所示…”相关的问题

更多“74LS290集成计数器的功能如表所示,其简化符号如图9所示…”相关的问题

.jpg)

的输出波形。

的输出波形。