题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

用十进制数中规模计数器设计一个可控计数器,当控制信号X=0时为模6计数,X=1时为模8计数,计数状态可以自己选

择。说明设计过程,画出逻辑图。

以上设计可以使用外加的逻辑门。

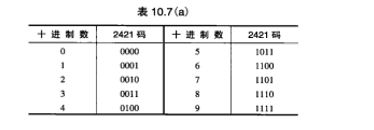

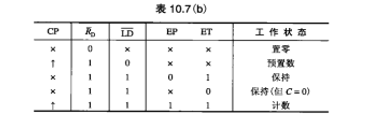

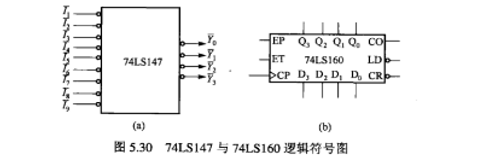

下表是十进制中规模计数器的功能表。

| RESET | bar{LOAD} | CLK | QDQCQBQA |

| 1 | 1 | φ | 复位全0状态 |

| φ | 0 | ↑ | 预置 |

| φ | 1 | ↑ | 加计数 |

计数器还有进位输出F端,当加计数剑1001状态时产生进位负脉冲输出。

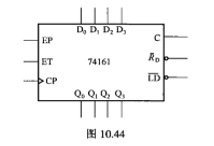

计数器的逻辑符号如图所示。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“用十进制数中规模计数器设计一个可控计数器,当控制信号X=0时…”相关的问题

更多“用十进制数中规模计数器设计一个可控计数器,当控制信号X=0时…”相关的问题

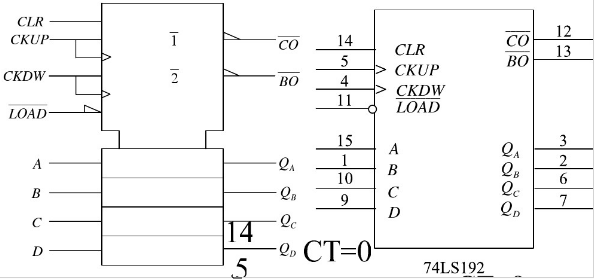

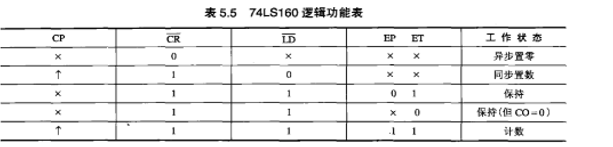

是进位输出,加法计数进入状态1001后产生一个周期宽度的负脉冲输出。借位输出是

是进位输出,加法计数进入状态1001后产生一个周期宽度的负脉冲输出。借位输出是 ,减法计数进入状态0000后产生一个周期宽度的负脉冲输出。如图为74LS192构成的计数器,74LS1l92功能表如表所示。解答如下问题:

,减法计数进入状态0000后产生一个周期宽度的负脉冲输出。如图为74LS192构成的计数器,74LS1l92功能表如表所示。解答如下问题: