题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

分析图所示的由中规模右移位寄存器74LS195和数据选择器74LS153组成的时序逻辑电路。画出状态转移图(以QA、QB、

分析图所示的由中规模右移位寄存器74LS195和数据选择器74LS153组成的时序逻辑电路。画出状态转移图(以QA、QB、QC、QD的顺序表示),分析电路的功能。74LS195已经处于移位的工作状态。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

分析图所示的由中规模右移位寄存器74LS195和数据选择器74LS153组成的时序逻辑电路。画出状态转移图(以QA、QB、QC、QD的顺序表示),分析电路的功能。74LS195已经处于移位的工作状态。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“分析图所示的由中规模右移位寄存器74LS195和数据选择器7…”相关的问题

更多“分析图所示的由中规模右移位寄存器74LS195和数据选择器7…”相关的问题

已知所有的反相器均为74LS系列TIL电路,输入电流IIL=0.4mA,

IH=20μA,IOL(max)=8mA,IOH(max)=0.4mA.

图2.3.15(a)、(b)所示的逻辑门电路均为+5 V电源供电,在下列两种情况下,分别讨论图2.3.15(a)、(b)的输出各是什么? (1)两个电路均为CMOS门;

1.jpg) (2)两个电路均为74LS系列TTL门,VIL(max)=0.8 V,VIH(min)=2 V。

(2)两个电路均为74LS系列TTL门,VIL(max)=0.8 V,VIH(min)=2 V。

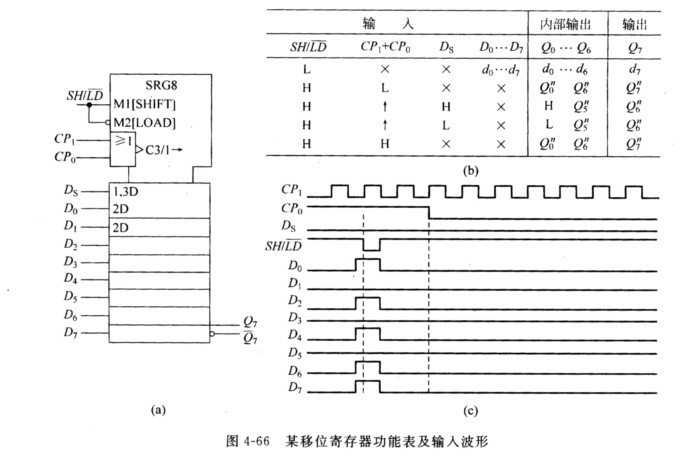

已知集成移位寄存器的逻辑符号功能表如图4-66(a)、(b)所示,试画出在图4-66(c)所示信号作用下Q7、

的输出波形。

的输出波形。

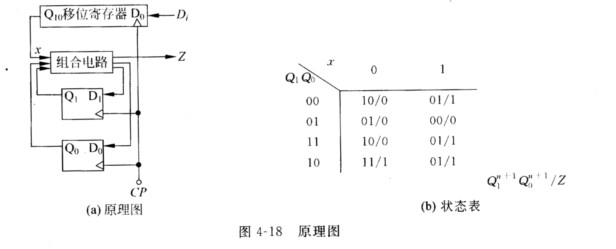

图4-18电路由一个11位移位寄存器和时序电路构成,移位寄存器寄存信息11 000011101且自右向左移位输出串行信号x,作用到时序电路输入端,再对外输出x。时序电路状态表如图4-18(b),初态00,试作出时序电路状态输出Q1、Q2和外输出z波形图。

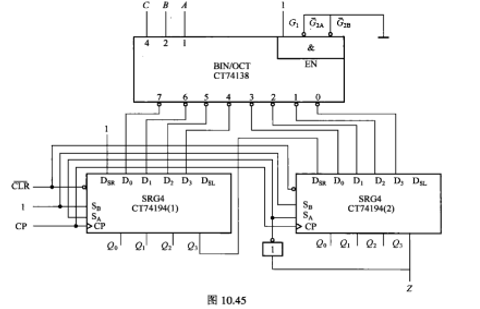

CT74194的初态均为0000,CBA=100,试画出在连续10个CP脉冲作用下对应输出Z的波形图.在原图上增加一个D触发器,实现14分频功能,并要求输出波形为方波.请问,D触发器和原图该如何连接,CBA应接什么信号.(说明D触发器和原图连接时,不必画原图,只要在D触发器上标注和原图相连的信号,并注明输出端)

图11-20是一个四位右移寄存器,其输入信号波形和时钟脉冲波形如图11-30(a)所示,试根据输入信号波形和时钟脉冲波形画出移位寄存器的各位输出端的波形图。设移位寄存器的初始状态Q3、Q2、Q1、Q0均为“0”。

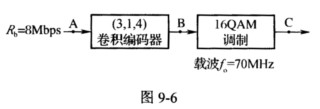

取值1、0的二进制独立等概序列经(3,1,4)卷积编码(卷积编码器的约束长度K=4,移位寄存器级数为m=K-4=3)后,送至16QAM数字调制器,如图9-6所示。已知此卷积码的生成多项式是g1(x)=1,g2(x)=l+x2+x3, g3(x)=l+x+x2+x3。 (1)画出卷积码编码器电路; (2)求出图9-6中B、C处的码元速率,画出C点的功率谱密度图;

(3)画出16QAM的信号空间图,并求出星座图中最小的欧式距离平方和平均能量之比(假设采用常规矩形星座,各星座点等概出现)。

(3)画出16QAM的信号空间图,并求出星座图中最小的欧式距离平方和平均能量之比(假设采用常规矩形星座,各星座点等概出现)。

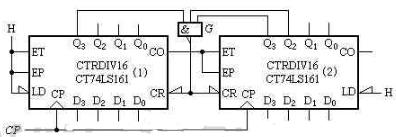

分析图所示的由两片中规模同步计数器CT74LS161构成的计数分频器的模值。第(1)片CT74LS161为低位计数器,第(2)片CT74LS161为高位计数器。

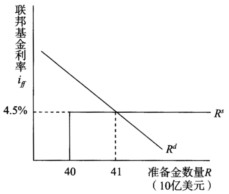

A.利用图17A所示的准备金市场填空:

非借入准备金=____________ 贴现贷款的规模=____________ 联邦基金利率=______% 贴现率=______% B.解释为什么当联邦基金利率下跌到4.5%以下时,贴现贷款为零?

非借入准备金=____________ 贴现贷款的规模=____________ 联邦基金利率=______% 贴现率=______% B.解释为什么当联邦基金利率下跌到4.5%以下时,贴现贷款为零?