题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

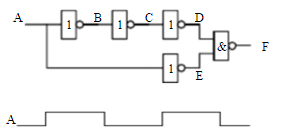

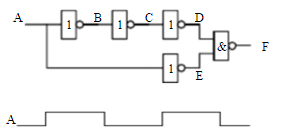

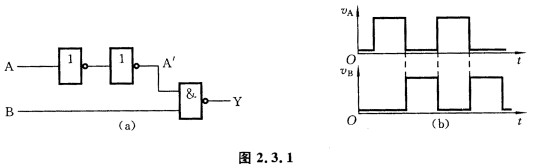

试画出图中所示电路中各点在考虑门电路有延迟情况下的波形。各逻辑门平均传输延迟为10ns。输入信号A的周期为1

00ns。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

00ns。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“试画出图中所示电路中各点在考虑门电路有延迟情况下的波形。各逻…”相关的问题

更多“试画出图中所示电路中各点在考虑门电路有延迟情况下的波形。各逻…”相关的问题

图2.3.5所示电路中,(a)图中的G1、G2均为CMOS门电路;(b)图中G1、G2和G3均为TTL门电路,G4为CMOS门电路。试写出Y1和Y2的逻辑表达式。

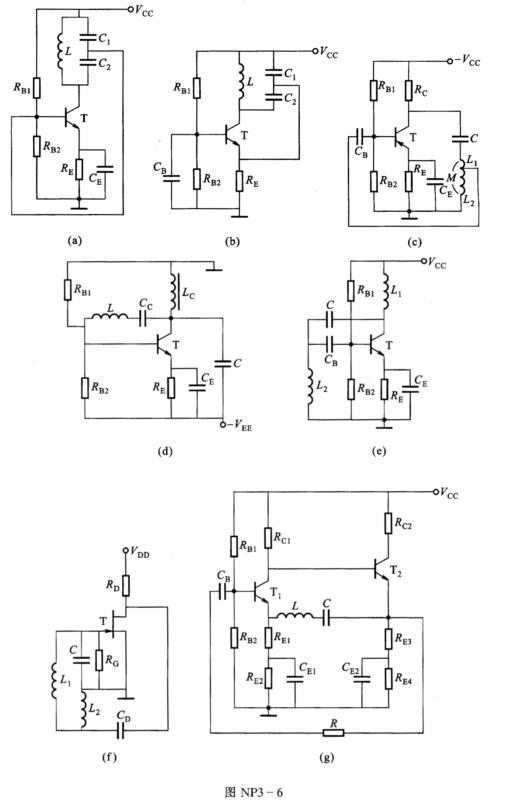

试画出图NP3-6所示各振荡器的交流通路,并判断哪些电路可能产生振荡,哪些电路不能产生振荡。图中,CB、CC、CE、CD为交流旁路电容或隔直流电容,LC为高频扼流圈,偏置电阻RB1、RB2、RG不计。

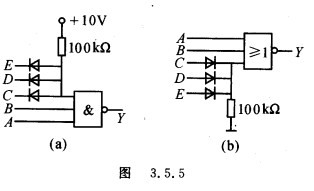

在CMOS门电路中,有时采用图3.5.5所示的方法扩展输入端。试分析图中(a),(b)所示电路的逻辑功能,写出Y的逻辑表达式。假定VDD=10 V,二极管的正向导通压降VD=0.7 V。

试分析图3.5.7(a),(b)所示电路的逻辑功能,写出y的逻辑表达式。图中的门电路均为CMOS门电路。

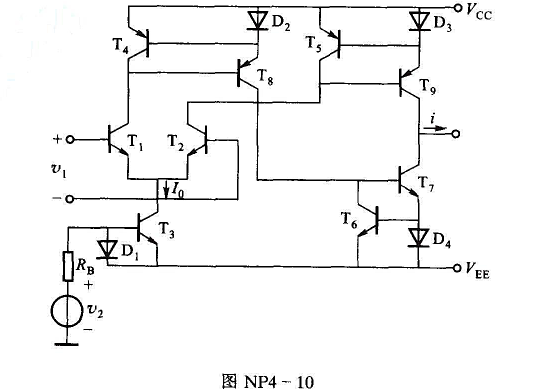

图NP4- 10所示为单差分对管电路,图中T1~T3、D1组成差分放大器, 组成三个电流源电路,若各管β足够大,VBE(on)可忽略,试导出输出电流i的表达式。若

组成三个电流源电路,若各管β足够大,VBE(on)可忽略,试导出输出电流i的表达式。若

,试画出下列两种情况下的输出电流i的波形及其频谱图:(1)V1m很小,处于小信号工作状态;(2)V1m很大,处于开关工作状态。

,试画出下列两种情况下的输出电流i的波形及其频谱图:(1)V1m很小,处于小信号工作状态;(2)V1m很大,处于开关工作状态。

画出图2.3.1所示电路在下列两种情况下的输出电压波形: (1)忽略所有门电路的传输延迟时间; (2)考虑每个门电路的传输延迟时间都为tpd

图NP4-10所示为单差分对管电路,图中T1-T3,D1组成差分放大器,T4,T8,D2,T5,D9,T3和T6,T7,D4组成三个电流源电路,若各管β足够大,VBE(on)可忽略,试导出输出电流i的表达式。若v1(t)=V1mcosωct,v2(t)=V2mcosΩt,且V2m< |VEE|,试画出下列两种情况下的输出电流i的波形及其频谱图:(1)V1m很小,处于小信号工作状态;(2)V1m很大,处于开关工作状态。