题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

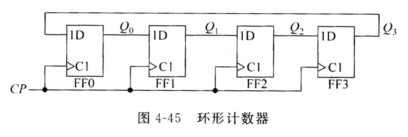

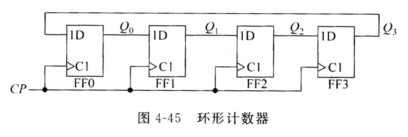

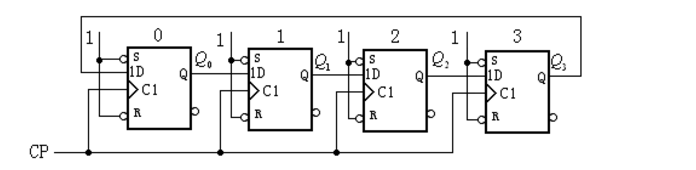

图4-45所示为一环形计数器。如果电路的初始状态为Q3Q2Q1Q0=1000,试画出在一系列CP脉冲作用下Q3、Q2

图4-45所示为一环形计数器。如果电路的初始状态为Q3Q2Q1Q0=1000,试画出在一系列CP脉冲作用下Q3、Q2、Q1以及Q0的波形。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图4-45所示为一环形计数器。如果电路的初始状态为Q3Q2Q1Q0=1000,试画出在一系列CP脉冲作用下Q3、Q2、Q1以及Q0的波形。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“图4-45所示为一环形计数器。如果电路的初始状态为Q3Q2Q…”相关的问题

更多“图4-45所示为一环形计数器。如果电路的初始状态为Q3Q2Q…”相关的问题

图4-47所示为一扭环形计数器。如果电路的初始状态为Q3Q2Q1Q0=0000,试画出在一系列CP脉冲作用下Q3、Q2、Q1和Q0的波形。为什么说它是一个计数器?它的模是几?该电路是自启动的吗?

.jpg)

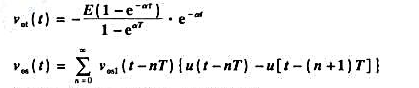

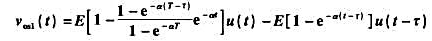

t)之特点.已求得v0(t)由瞬态响应 和稳态响应

和稳态响应 两部分组成,其表达式分别为:

两部分组成,其表达式分别为:

其中 为

为 第一周期的信号

第一周期的信号

(1)画出v0(t)波形,从物理概念讨论波形特点;

(2)试用拉氏变换方法求出上述结果;

(3)系统函数极点分布和激励信号极点分布对响应结果特点有何影响.

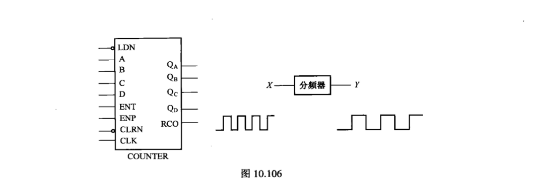

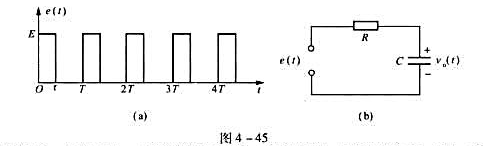

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1 MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

图8.2.1(a)所示为产生宽度等于12个CP周期的脉冲产生器,试选择MSI计数器设计控制电路,并画出电路的工作波形。

如图所示为一扭环形计数器。如果电路的初始状态为Q3Q2Q1Q0=1000,试画出在一系列CP脉冲作用下Q3、Q2、Q1和Q0的波形。为什么说它是一个计数器?它的模是几?该电路是自启动的吗?

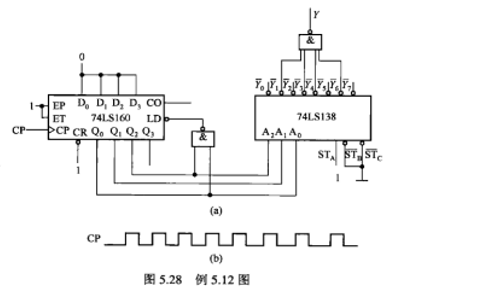

图(a)所示电路为同步十进制加法计数器74160和3线-8线译码器74138组成的电路,74138输出低电平有效,使能端

有效,使能端处于有效状态.

(1)74160构成多少进制计数器.

(2)假定74160初始状态Q3Q2Q1Q0=0000,试对应图5.28(b)的CP脉冲图画出Q3、Q2、Q1、Q0和Y的输出波形.

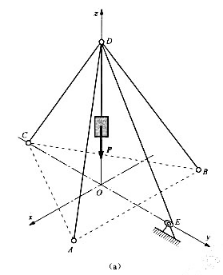

轮由绞车E牵引将重为P=30kN的物体吊起。绞车位于∠ACB的角平分线y轴上,绳索DE与水平面的夹角为60°。不计构件重量,当重物被匀速提升时,求各脚所受的力。

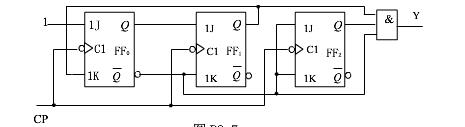

分析图所示的计数电路,画出电路的状态转换图(只画有效状态),并说明其为多少进制的计数器。