题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

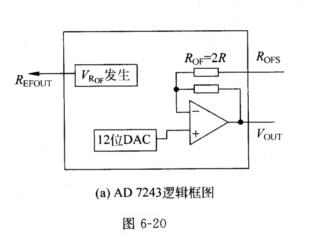

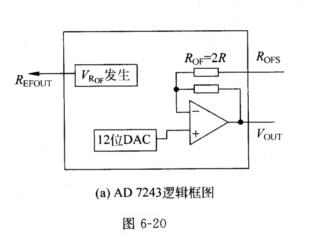

图6-20(a)是AD 7243逻辑框图,它是一种可供用户由单极性扩展为双极性的DAC集成芯片,单极性输出为0

图6-20(a)是AD 7243逻辑框图,它是一种可供用户由单极性扩展为双极性的DAC集成芯片,单极性输出为0→+10V,请读者增加适当的引脚连接线,使之成为一5V→+5V双极性输出的DAC,并说明理由。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图6-20(a)是AD 7243逻辑框图,它是一种可供用户由单极性扩展为双极性的DAC集成芯片,单极性输出为0→+10V,请读者增加适当的引脚连接线,使之成为一5V→+5V双极性输出的DAC,并说明理由。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“图6-20(a)是AD 7243逻辑框图,它是一种可供用户由…”相关的问题

更多“图6-20(a)是AD 7243逻辑框图,它是一种可供用户由…”相关的问题

图(a)是AD7243逻辑框图,它是一种可供用户由单极性扩展为双极性的DAC集成芯片,单极性输出为0→+10V,请读者增加适当的引脚连接线,使之成为-5V→+5V双极性输出的DAC,并说明理由。

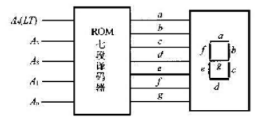

图22.17是用ROM构成的七段译码电路框图。A4~A0为ROM的输入端。A3~A0是数据输入端,最高位A4只用作试灯输入端(LT)。当LT=1时,不论二进制数码A3A2A1A0为何值,数码管七段全亮。当LT=0时,数码管则显示四位二进制数所对应的十进制数码。半导体数码管为共阴极接法。试列出实现上述逻辑要求的ROM功能表,并画出ROM的阵列图。

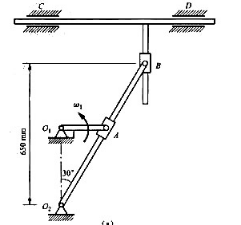

的速度和加速度.

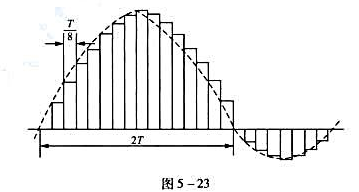

数宽度截取8T(中心向左右对称),矩形窄脉冲宽度T/8.每当一个“1"码到来时(由速率为2π/T的窄脉冲控制)即出现Sa码波形(峰值延后4T).

(1)画出此系统逻辑框图和主要波形;

(2)考虑此系统是否容易实现;

(3)在得到上述信号之后,若要去除波形中的小阶梯,产生更接近连续Sa函数的波形需采取什么办法?