题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

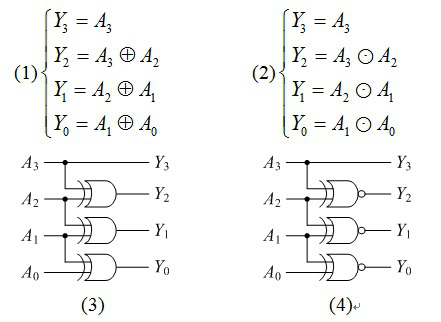

设计一个代码转换电路,要求输入为4位自然二进制码,输出为4位循环码。根据题意,符合设计要求的逻辑函数表达式和逻辑电路是()。

A.(1)和(3)

B.(1)和(4)

C.(2)和(3)

D.(2)和(4)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.(1)和(3)

B.(1)和(4)

C.(2)和(3)

D.(2)和(4)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“设计一个代码转换电路,要求输入为4位自然二进制码,输出为4位…”相关的问题

更多“设计一个代码转换电路,要求输入为4位自然二进制码,输出为4位…”相关的问题

为4位8421BCD码表达的数量:要求该电路实现下列功能:当输入小于5时,输出等于输入加2:当输入大于等于5时,输出等于输入减3。要求写出各输出逻辑函数的最小项和表达式。

试用一片超前进位4位全加器CC4008,将4位二进制码转换成8421BCD码。

提示 在输入代码为0000~1001时,二码相同;当输入二进制码为1010~1111时须变为2位BCD码,逢十进1,即“1010(2)”变为“10000(BCD)”、“1011(2)”变为“10001(BCD)”……“1111(2)”变为“10101(BCD)”,如果把后者也看成二进制码,则与转换前恒差6。

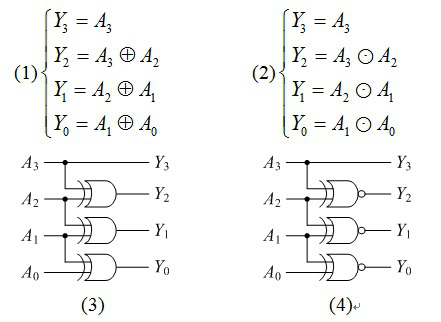

二进制码和循环码的对应关系如表所列。

(1)分别求解两种情况下输出函数的逻辑表达式;

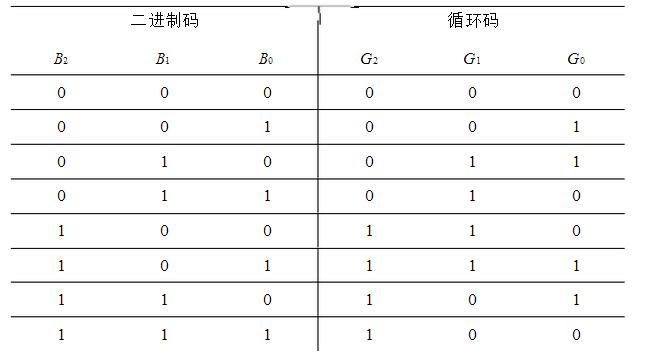

(2)检查电路有无错误,若有则改正。

已知4位数值比较器74LS85的传输延迟时间(从加上两个输入比较数到产生输出比较结果所需时间)小于45ns。要求用6片74LS85接成一个24位数值比较电路,传输延迟时间不得大于90ns。

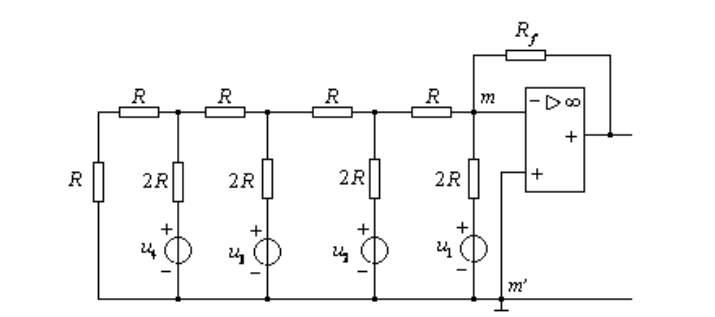

电路如图所示,设Rf=16R,验证该电路的输出uo与输入u1~u4之间的关系为uo=-(8u1+4u2+2u3+u4)。[注:该电路为4位数字-模拟转换器,常用在信息处理、自动控制领域。该电路可将一个4位二进制数字信号转换成模拟信号,例如当数字信号为1101时,令u1=u2=u4=1,u3=0,则由关系式uo=-(8u1+4u2+2u3+u4)得模拟信号uo=-(8+4+0+1)=-13。]

用JK触发器和门电路设计一个4位格雷码计数器,它的状态转换表应如表6.32所示。

| 表6.32 | |||||

| 计数 顺序 | 电路状态 | 进位 输出C | |||

| Q3 | Q2 | Q1 | Q0 | ||

| 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 | 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 | 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 | 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 | 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 |

1.jpg) 试求一个Z脉冲周期内应包含多少个CP脉冲周期。

试求一个Z脉冲周期内应包含多少个CP脉冲周期。

2.jpg)