更多“设计一个4-10线译码器,其输入为8421BCD码。设输入、…”相关的问题

更多“设计一个4-10线译码器,其输入为8421BCD码。设输入、…”相关的问题

第2题

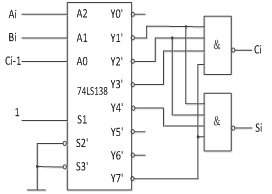

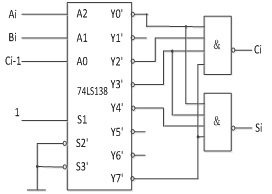

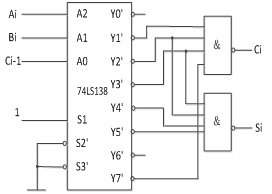

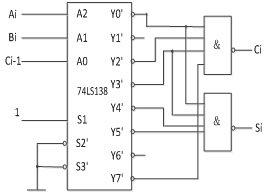

试用3线-8线译码器和门电路设计1位二进制全减器电路。其中,输入为被减数(Ai)、减数(Bi)和来自低位的借位(Ci-1);输出为两数之差(Si)和向高位的借位信号(Ci)。则正确的电路设计是:

A.

B.

C.

D.

第3题

试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。该电路输入X,输出F均为3位二进制数。二者之间关

试用输出低电平有效的3线-8线译码器和逻辑门设计一组合电路。该电路输入X,输出F均为3位二进制数。二者之间关系如下:

2≤X≤5时,F=X+2

X<2时,F=1

X>5时,F=0

第4题

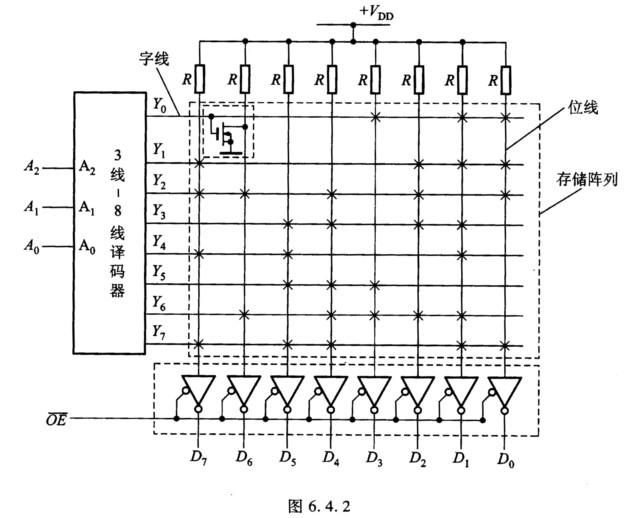

一个NMOS—ROM存储矩阵如图6.4.2所示。图中存储阵列的“×”表示字线和位线间接有NMOS管,接法见左上方

的虚线框。

点击查看答案

(1)若地址译码器的输入A2A1A0取值为000、001、010、…、111时,其相应的输出Y0、Y1、Y2、…、Y7为高电平。试问输入A2A1A为010、011、101时,ROM相应的输出状态是什么? (2)若已知ROM的输出为10110011,试问地址译码器的输入A2A1A0应该是什么状态?

(1)若地址译码器的输入A2A1A0取值为000、001、010、…、111时,其相应的输出Y0、Y1、Y2、…、Y7为高电平。试问输入A2A1A为010、011、101时,ROM相应的输出状态是什么? (2)若已知ROM的输出为10110011,试问地址译码器的输入A2A1A0应该是什么状态?

第5题

用GAL16V8设计一个3-8线译码器,该译码器带有一个低电平有效和一个高电平有效的使能端。试写出相应的VHDL语言

用GAL16V8设计一个3-8线译码器,该译码器带有一个低电平有效和一个高电平有效的使能端。试写出相应的VHDL语言程序。

第6题

2线-4线译码器74Z139的输入为高电平有效,使能输入及输出均为低电平有效。试用74X139构成4线-16线译码器。

2线-4线译码器74Z139的输入为高电平有效,使能输入及输出均为低电平有效。试用74X139构成4线-16线译码器。

第7题

TTL集成电路74LS138是3/8线译码器,译码器是输出低电平有效,若输入为A2A1A0=101时,输出Y7-Y0为()。

A.00100000

B.11011111

C.11110111

D.00000100

第8题

用3线—8线译码器设计一个既能做一位二进制数的令加运算,又能做一位二进制数的伞减运算的电路。 要求:(1)根

用3线—8线译码器设计一个既能做一位二进制数的令加运算,又能做一位二进制数的伞减运算的电路。

要求:(1)根据题意要求,写真值表。

(2)写出电路输出函数的最简与或表达式。

(3)画出用3线—8线译码器74LS138芯片实现的电路。

第9题

设计一个组合逻辑电路,当M=1时,两个2位二进制数A=A1A0和B=B180实现全加;当M=0时,两个二进制数实现全减。要求

设计一个组合逻辑电路,当M=1时,两个2位二进制数A=A1A0和B=B180实现全加;当M=0时,两个二进制数实现全减。要求用两片3线-8线译码器74HC138实现,必要时可用门电路。

如果结果不匹配,请

如果结果不匹配,请