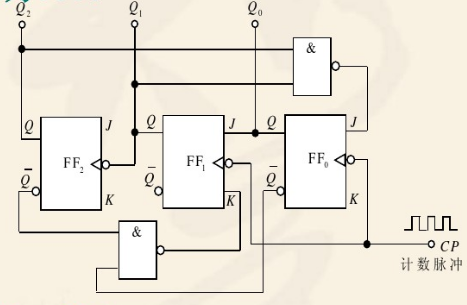

更多“试分析下图所示电路是几进制计数器,画出各触发器输出端的波形图…”相关的问题

更多“试分析下图所示电路是几进制计数器,画出各触发器输出端的波形图…”相关的问题

第2题

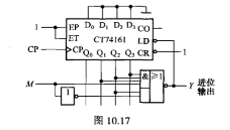

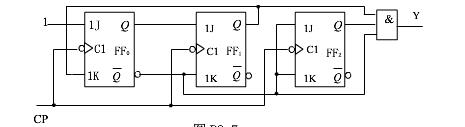

分析图6-13所示电路,画出74HC161Q3Q2Q1Q0的状态转换图,说明74HC161构成几进制计数器。假设Q3Q2Q1Q0的初始状

分析图6-13所示电路,画出74HC161Q3Q2Q1Q0的状态转换图,说明74HC161构成几进制计数器。假设Q3Q2Q1Q0的初始状态均为0。

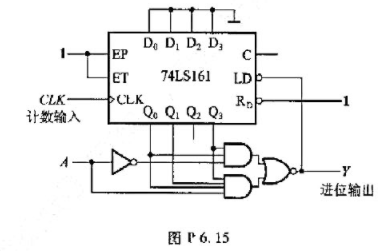

第5题

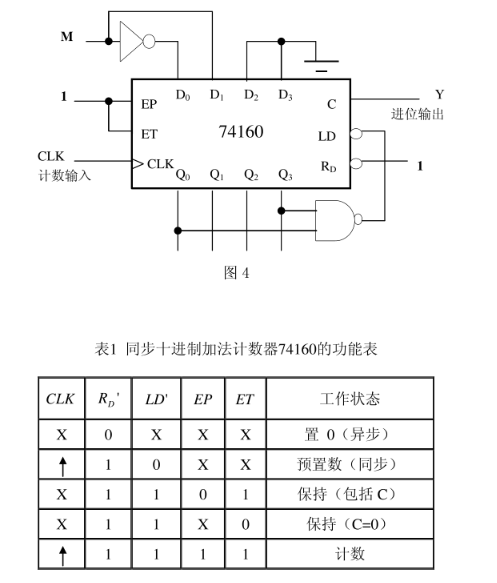

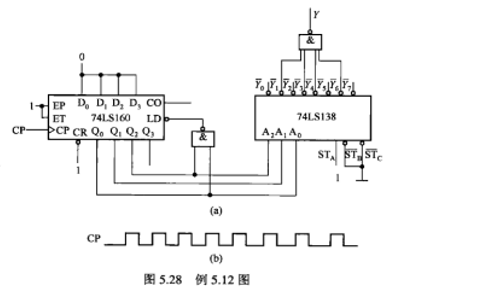

图5.28(a)所示电路为同步十进制加法计数器74160和3-8译码器74138组成的电路,74138输出低电平

图5.28(a)所示电路为同步十进制加法计数器74160和3-8译码器74138组成的电路,74138输出低电平

点击查看答案

有效,使能端处于有效状态.

(1)74160构成多少进制计数器.

(2)假定74160初始状态Q3Q2Q1Q0=0000,试对应图5.28(b)的CP脉冲图画出Q3、Q2、Q1、Q0和Y的输出波形.

第6题

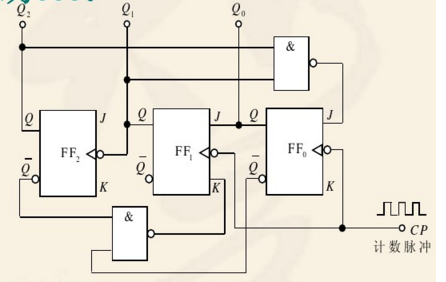

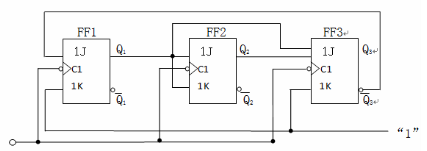

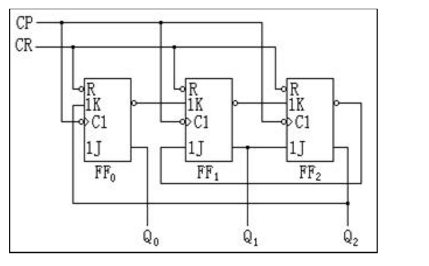

分析图所示的计数电路,画出电路的状态转换图(只画有效状态),并说明其为多少进制的计数器。

分析图所示的计数电路,画出电路的状态转换图(只画有效状态),并说明其为多少进制的计数器。

如果结果不匹配,请

如果结果不匹配,请