题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

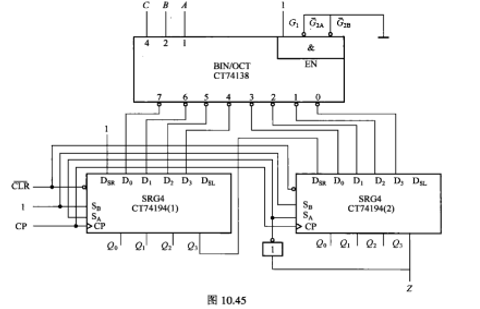

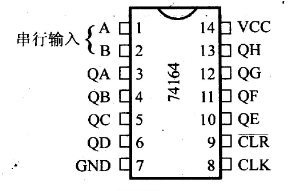

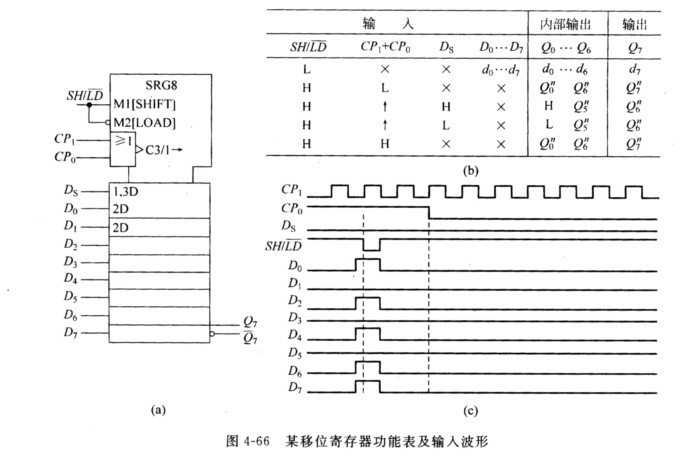

74164的符号图和功能表见图14和下表。逻辑电路如图15所示,其中RA、RB和RS均为74164,其余电路为全加器和D触发

74164的符号图和功能表见图14和下表。逻辑电路如图15所示,其中RA、RB和RS均为74164,其余电路为全加器和D触发器,要求:

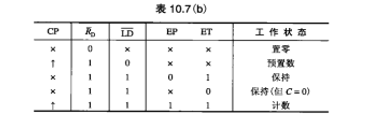

| bar{CR} | CP | D0=SASB | Q0Q1…Q7 |

| 0 | × | × | 0 0…0 |

| 1 | ↑ | 0 | 0 Q0…Q6 |

| 1 | ↑ | 1 | 1 Q0…Q6 |

(1)8个CP脉冲后,RA、RB和RS中的内容Q7Q6…Q0分别为?

(2)再来8个CP脉冲后,RA、RB和RS中的内容Q7Q6…Q0分别为?

(3)该电路实现了什么功能?

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“74164的符号图和功能表见图14和下表。逻辑电路如图15所…”相关的问题

更多“74164的符号图和功能表见图14和下表。逻辑电路如图15所…”相关的问题

1.jpg)

1.jpg)

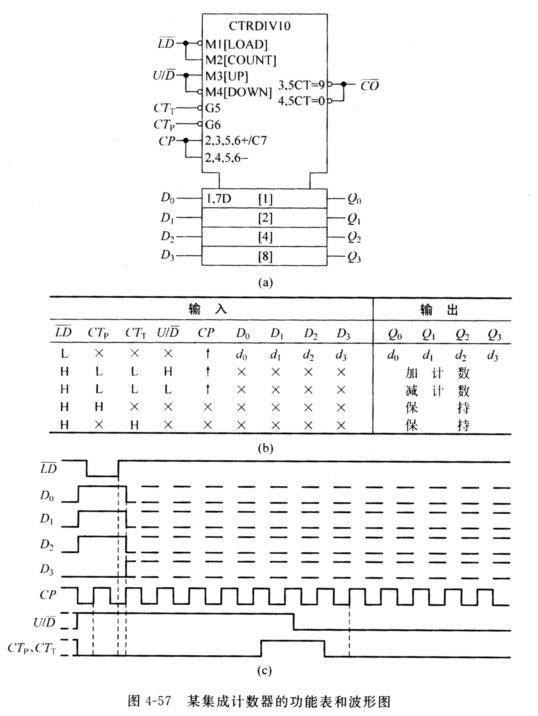

的输出波形。

的输出波形。

的输出波形。

的输出波形。