更多“TTL集电极开路门(OC门)和CMOS漏极开路门(OD门)…”相关的问题

更多“TTL集电极开路门(OC门)和CMOS漏极开路门(OD门)…”相关的问题

第3题

电路如图2.4.16(a)所示。已知当三极管导通时Vbe=0.7V,饱和时Vces=0.3V,β=100;OC门G1输出管截止时的漏电流约

电路如图2.4.16(a)所示。已知当三极管导通时Vbe=0.7V,饱和时Vces=0.3V,β=100;OC门G1输出管截止时的漏电流约为50μA,饱和导通时最大允许灌电流ILM=10mA,输出低电平VOL=0.3V;TTL与非门输入特性如图(b)所示。要求三极管集电极输出端P为高电平时VPH=3.5V,低电平时VPL=0.3V。试问:

第4题

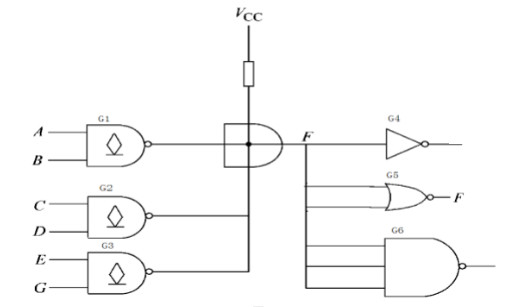

在图P3.17电路中,OC门G1~G3输出高电平时集电极开路三极管的漏电流最大值为IOH(max)=0.25mA;低电平最大输出

在图P3.17电路中,OC门G1~G3输出高电平时集电极开路三极管的漏电流最大值为IOH(max)=0.25mA;低电平最大输出电流IOL(max)=16mA,低电平最大值为VOL(max)=0.2V。门电路G4~G6的高电平输入电流最大值为IIH(max)=40μA,低电平输入电流最大值为IIL(max)=-1.6mA。在满足VOH≥3.6V、VOL≤0.2V的条件下,允许RP的取值范围有多大?

第6题

TTL门驱动CMOS门时,如果不满足VOH(min)≥VIH(min),常用的解决方法是____________。

TTL门驱动CMOS门时,如果不满足VOH(min)≥VIH(min),常用的解决方法是____________。

第7题

CMOS门驱动TTL门时,如果不满足IOL(max)≥IIL(total),常用的解决方法是 ____________或 __________

CMOS门驱动TTL门时,如果不满足IOL(max)≥IIL(total),常用的解决方法是 ____________或 ____________ 。

第11题

逻辑电路如图2.4.9所示。 (1)写出各电路名称: (2)当其为CMOS门时,写出输出表达式;

逻辑电路如图2.4.9所示。

(1)写出各电路名称: (2)当其为CMOS门时,写出输出表达式; (3)当其为TTL门时,写出输出表达式。

(1)写出各电路名称: (2)当其为CMOS门时,写出输出表达式; (3)当其为TTL门时,写出输出表达式。

如果结果不匹配,请

如果结果不匹配,请