题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

某计算机的指令流水线由4个功能段组成,指令流经各功能段的时间(忽略各功能段之间的缓存时间)分别

某计算机的指令流水线由4个功能段组成,指令流经各功能段的时间(忽略各功能段之间的缓存时间)分别为90ns、80ns、70ns、和60ns,则该计算机的CPU时钟周期至少是()。

A.90ns

B.80ns

C.70ns

D.60ns

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

某计算机的指令流水线由4个功能段组成,指令流经各功能段的时间(忽略各功能段之间的缓存时间)分别为90ns、80ns、70ns、和60ns,则该计算机的CPU时钟周期至少是()。

A.90ns

B.80ns

C.70ns

D.60ns

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“某计算机的指令流水线由4个功能段组成,指令流经各功能段的时间…”相关的问题

更多“某计算机的指令流水线由4个功能段组成,指令流经各功能段的时间…”相关的问题

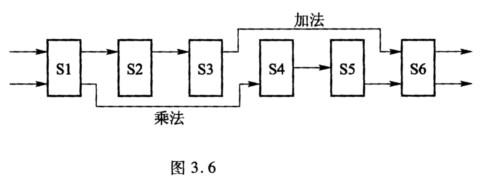

有一条动态多功能流水线由6个功能段组成,如图3.6所示。

图3.6 其中,S1、S4、S5、S6组成乘法流水线,S1、S2、S3、S6组成加法流水线,各个功能段时间均为50 ns,假设该流水线的输出结果可以直接返回输入端,而且设置有足够的缓冲寄存器,若以最快的方式用该流水线计算

图3.6 其中,S1、S4、S5、S6组成乘法流水线,S1、S2、S3、S6组成加法流水线,各个功能段时间均为50 ns,假设该流水线的输出结果可以直接返回输入端,而且设置有足够的缓冲寄存器,若以最快的方式用该流水线计算

xiyizi。

xiyizi。

在没有任何其他定向(或旁路)硬件的支持下,请画出该指令序列执行的流水线时空图。假设采用排空流水线的策略处理分支指令,且所有的存储器访问都命中Cache,那么执行上述循环需要多少个时钟周期?

用一台每个时钟周期发射两条指令的超标量处理机运行下面一段程序。所有指令都要进行取指(IF)、译码(ID)、执行、写结果(WB)4个阶段。其中IF、ID、WB这3个阶段各为一个流水段,其延迟时间都为10 ns。在执行阶段,LOAD操作、AND操作各延迟10 ns,ADD操作延迟20 ns,MUL操作延迟30 ns。这4种功能部件各设置一个,它们可以并行工作。ADD部件和MUL部件都采用流水结构,每一级流水线的延迟时间都是10 ns。 I1 LOAD R0,M(A) ;R0←M(A) I2 ADD R1,R0 ;R1←(R1)+(R0) I3 LOAD R2,M(B) ;R2←M(B) I4 MUL R3,R4 ;R3←(R3)×(R4) I5 AND R4,R5 ;R4←(R4)∧(R5) I6 ADD R2,R5 ;R2←(R2)+(R5) ①请列出程序代码中所有的数据相关及其相关类型。 ②假设所有运算型指令都在译码(ID)流水段读寄存器,在写结果(WB)流水段写寄存器,采用顺序发射、顺序完成的调度方法。画出流水线的时空图,计算执行这个程序所用的时间。

A.流水线由若干段组成

B.流水线每段的时间应尽量相等

C.流水线的段数越多越好

D.流水线吞吐率与最慢段的延迟有关

E.流过流水线的指令越多,流水线吞吐率越高

F.流水线深度一般就是指流水线段数G、流水线最大加速比等于流水线段数H、流过流水线的指令越多,流水线效率越高

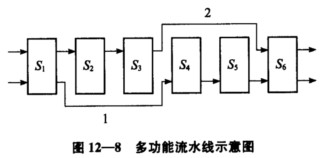

如图12—8所示,一个动态多功能流水线由6个功能段组成。

其中:S1、S4、S5、S6组成乘法流水线,S1、S2、S3、S6组成加法流水线,每个功能段时间均为50ns。假定该流水线的输出结果可以直接返回流水线输入端,而且设置有足够的缓冲寄存器。若按照最快的方式用该流水线计算f=

其中:S1、S4、S5、S6组成乘法流水线,S1、S2、S3、S6组成加法流水线,每个功能段时间均为50ns。假定该流水线的输出结果可以直接返回流水线输入端,而且设置有足够的缓冲寄存器。若按照最快的方式用该流水线计算f=

xiyizi。请画出其处理过程的时空图。并计算其实际吞吐率、加速比和效率。

xiyizi。请画出其处理过程的时空图。并计算其实际吞吐率、加速比和效率。

假设指令流水线分取指(IF)、译码(ID)、执行(EX)、回写(WR)四个过程段,共有10条指令连续输入此流水线。 (1)画出指令周期流程。 (2)画出非流水线时空图。 (3)画出流水线时空图。 (4)假设时钟周期为100 ns,求流水线的实际吞吐量(单位时间执行完毕的指令数)。 (5)求该流水处理器的加速比。

模型计算机CPU的运算器由哪些主要电路组成?在执行ADC和SBB指令时,ALU的功能选择信号M1、M0是什么状态?AKU进位输入信号CL的状态来自哪里?

下列关于动态流水线正确的是()。

A.动态流水线是在同一时间内,当某些段正在实现某种运算时,另一些段却正在进行另一种运算,这样对提高流水线的效率很有好处,但会使流水线控制变得很复杂

B.动态流水线是指运算操作并行

C.动态流水线是指指令步骤并行

D.动态流水线是指程序步骤并行