更多“由8选1数据选择器实现的函数F如图所示。”相关的问题

更多“由8选1数据选择器实现的函数F如图所示。”相关的问题

第1题

用8选1数据选择器实现下列函数(输入提供原变量和反变量):

用8选1数据选择器实现下列函数(输入提供原变量和反变量):

F=Σ(0,2,3,6,7)

F(A、B、C、D)= ∑(0、3、5、8、11、14)+ ∑Φ(1、6、12、13);

选CBA为地址D0=1 D1=0 D2=0 D3=1

D4=0 D5=1 D6=1 D7=0

第5题

如图所示逻辑电路由CT74161(同步四位二进制计数器)和CT74151(八选一数据选择器)组成。

如图所示逻辑电路由CT74161(同步四位二进制计数器)和CT74151(八选一数据选择器)组成。

第6题

用4个已经连接好的逻辑门及一个4选1数据选择器(如图A3-2所示)实现逻辑函数F(A,B,C,D)=∑m(4,5,6,7,8,13,14,1

用4个已经连接好的逻辑门及一个4选1数据选择器(如图A3-2所示)实现逻辑函数F(A,B,C,D)=∑m(4,5,6,7,8,13,14,15)。要求无0、1信号,也无反变量可作为输入,只有输入变量A、B、C和D可用,4个逻辑门中只有在标有①、②、③处可供连接。

第7题

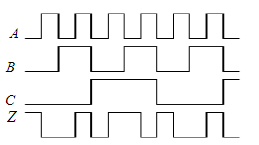

已知图3.2.103所示组合逻辑电路的输入和输出波形,试用一片4选1数据选择器实现此电路。要求:(1)写出输出函数Z

已知图3.2.103所示组合逻辑电路的输入和输出波形,试用一片4选1数据选择器实现此电路。要求:(1)写出输出函数Z的逻辑表达式:(2)画出逻辑线路图。

第8题

分别用8选1 MUX 741 5l和与非门实现函数F(A,B,C,D)=∑m(0,3,5,6,9,12,15)。

分别用8选1 MUX 741 5l和与非门实现函数F(A,B,C,D)=∑m(0,3,5,6,9,12,15)。

如果结果不匹配,请

如果结果不匹配,请