更多“如图是一序列信号发生器电路,它由1个计数器和1个4选1数据选…”相关的问题

更多“如图是一序列信号发生器电路,它由1个计数器和1个4选1数据选…”相关的问题

第1题

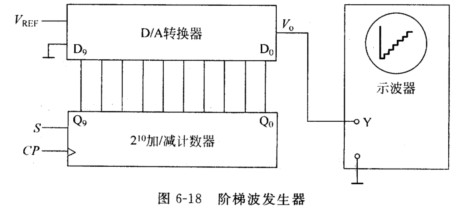

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1 MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

第2题

如图是用运算放大器构成的音频信号发生器的简化电路。已知图中R=1.6kΩ,C=0.1μF,R3=3.3kΩ,Rf1=1kΩ,Rf2=2kΩ。

如图是用运算放大器构成的音频信号发生器的简化电路。已知图中R=1.6kΩ,C=0.1μF,R3=3.3kΩ,Rf1=1kΩ,Rf2=2kΩ。

第3题

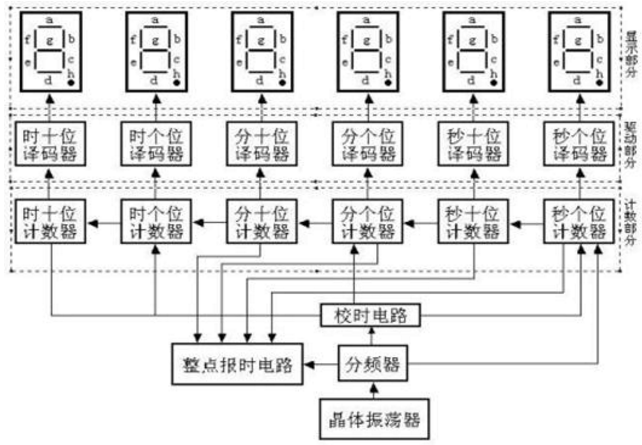

试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石英晶体振荡器(频率为32768Hz)加分频器来实现。译码

试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石英晶体振荡器(频率为32768Hz)加分频器来实现。译码显示电路将“时”、“分”、“秒”计数器的输出状态经七段显示译码器译码,通过6位LED七段显示器显示出来。整点报时电路是根据计时系统的输出状态产生一个脉冲信号,然后去触发音频发生器实现报时。校时电路是用来对“时”、“分”、“秒”显示数字进行校对调整的。

第4题

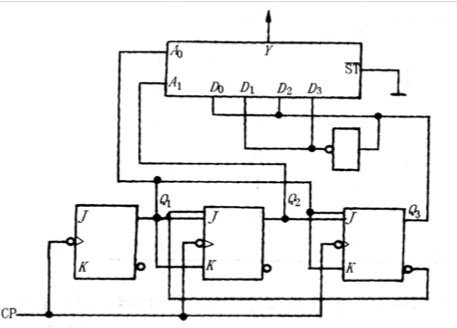

给出下列器件: 74LS194、74LS169、74LS161、74LS151及少量门电路,试设计一个输出序列为01001100010111的序列信号发生器。(1)采用反馈移位型结构实现电路。(2)采用计数型结构实现电路。

给出下列器件: 74LS194、74LS169、74LS161、74LS151及少量门电路,试设计一个输出序列为01001100010111的序列信号发生器。(1)采用反馈移位型结构实现电路。(2)采用计数型结构实现电路。

点击查看答案

第5题

设计一个同步时序逻辑电路,当输入信号X=0时,按二进制规律递增计数:当输入信号X=1时,按循环码计数,其状态转

换图如图(a)所示。要求用两个如图(b)所示的JK触发器及若干与或非门实现,且电路最简。

点击查看答案

第7题

x(n)是一个8点有限长序列,其8点DFT是它的Z变换X(z)在z平面的单位圆周上的8个等间隔点上的取样值,如图5.14所

x(n)是一个8点有限长序列,其8点DFT是它的Z变换X(z)在z平面的单位圆周上的8个等间隔点上的取样值,如图5.14所示。

现有一序列

试在图上标出y(n)的8点DFT所在位置。

如果结果不匹配,请

如果结果不匹配,请