题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

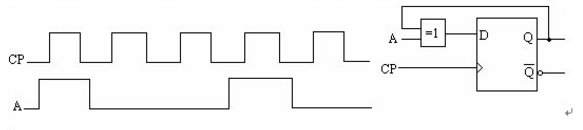

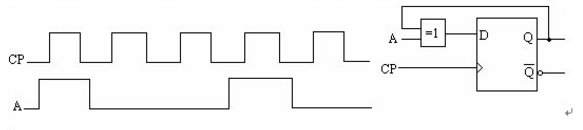

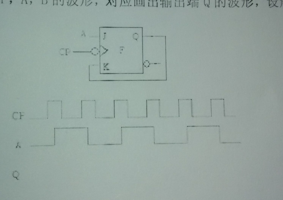

设维持-阻塞D触发器的初始状态为0,CP、A信号如下图所示,试画出触发器Q端的波形。

设维持-阻塞D触发器的初始状态为0,CP、A信号如下图所示,试画出触发器Q端的波形。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

设维持-阻塞D触发器的初始状态为0,CP、A信号如下图所示,试画出触发器Q端的波形。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“设维持-阻塞D触发器的初始状态为0,CP、A信号如下图所示,…”相关的问题

更多“设维持-阻塞D触发器的初始状态为0,CP、A信号如下图所示,…”相关的问题

D触发器组成的电路如图1.14(a)所示,设触发器的初始状态为“0”。时钟CP的波形如图1.14(b)所示,则输出Q端的波形为图1.14(b)中的( )。

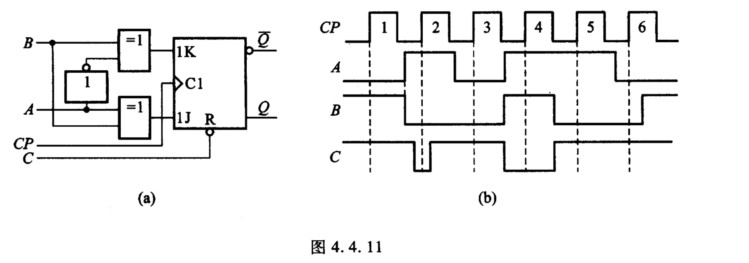

电路如图4.4.11(a)所示,若在A、B、CP端加入如图4.4.11(b)所示波形,设触发器初始状态为0,试画出Q端波形。

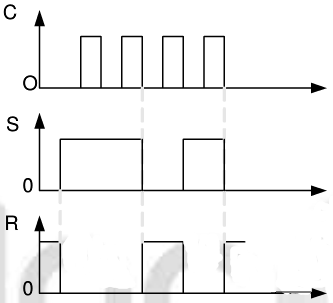

当可控RS触发器(见图21.1.4(a))的CP,S和R端加上图21.1.3所示的波形时,试画出Q端的输出波形。设初始状态为“0”和“1”两种情况。

图21-63为一时序逻辑电路,试列出Q2,Q1,Q0的状态真值表,并根据图示CP脉冲波形画出Q2,Q1,Q0的波形图(设各触发器Q端初始为0)。

电路如下图所示,已知CP和A的波形,画出触发器Q0、Q1及输出Vo的波形。设触发器的初始状态均为0。

试分析如图所示二个计数器的工作情况:

(1)写出各个JK触发器,J、K逻辑表达式。

(2)设各个触发器的初始状态为0,确定此时各个J、K端的状态。

(3)确定第一个CP作用后各个触发器的输出状态,以及各个J、K端的状态。

(4)依次确定下一个CP作用后各触发器的状态,以及各J、K端的状态,直至各个触发器的输出回到000为止。

(5)指出它们分别是几进制计数器(几个状态为一次循环则称为几进制计数器)。

如图题4.17所示电路中,FF1是JK触发器,FF2是D触发器,初始状态为0,试画出在CP作用下Q1、Q2的波形。

在图所示的同步D触发器中,加入图示的D和CP波形,画出触发器Q和