更多“能否用一片4位并行加法器74LS283将余3代码转换成842…”相关的问题

更多“能否用一片4位并行加法器74LS283将余3代码转换成842…”相关的问题

第2题

用4位加法器74LS283和4位2选1数据选择器74LS157设计一个可控码组转换器。当控制信号C=0时实现5421

码到8421码的转换;当C=1时实现2421码到842l码的转换。

点击查看答案

第3题

试用四位并行加法器74LS283设计一个加/减运算电路,当控制信号M=0时它将两个输入四位二进制数相加,而M=1时,

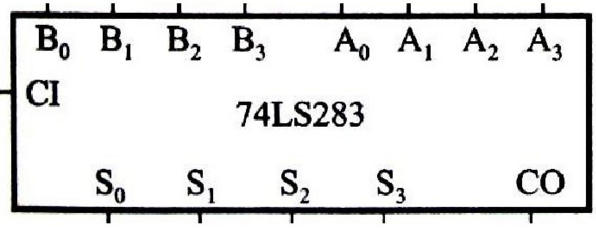

试用四位并行加法器74LS283设计一个加/减运算电路,当控制信号M=0时它将两个输入四位二进制数相加,而M=1时,它将两个四位二进制数相减。允许附加必要的门电路。74LS283的框图如图3.2.22所示。

第5题

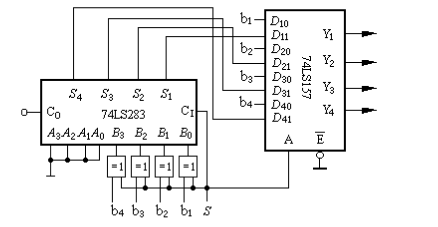

由4位超前进位加法器74LS283和4位2选1数据选择器74LS157组成的电路如下图所示,其中S为输入控制信号。试填写

下表所示的输入/输出对照表。

| 输入/输出对照表 | |||||||||||

| 输入 | S=0 | S=1 | |||||||||

| b4 | b3 | b2 | b1 | Y4 | Y3 | Y2 | Y1 | Y4 | Y3 | Y2 | Y1 |

| 0 | 0 | 0 | 0 | ||||||||

| 0 | 0 | 1 | 1 | ||||||||

| 0 | 1 | 0 | 1 | ||||||||

| 0 | 1 | 1 | 0 | ||||||||

| 1 | 0 | 0 | 1 | ||||||||

| 1 | 0 | 1 | 0 | ||||||||

| 1 | 1 | 0 | 0 | ||||||||

| 1 | 1 | 1 | 1 |

第7题

试利用两片4位二进制并行加法器741S283和必要的门电路.组成1位二-是进制加法器电路.(根据二-十进制数的加法运算规则,当两数之和小于、等于9(1001)时,相加的结果和按二进制数相加所得到的结果一样.当两数之和大于9(即等于1010~111)时,则应在按二进制数相加的结果上加6(0110),这样就以给出进位信号,同时得到一个小于9的和.)

试利用两片4位二进制并行加法器741S283和必要的门电路.组成1位二-是进制加法器电路.(根据二-十进制数的加法运算规则,当两数之和小于、等于9(1001)时,相加的结果和按二进制数相加所得到的结果一样.当两数之和大于9(即等于1010~111)时,则应在按二进制数相加的结果上加6(0110),这样就以给出进位信号,同时得到一个小于9的和.)

点击查看答案

如果结果不匹配,请

如果结果不匹配,请

1.jpg)