题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

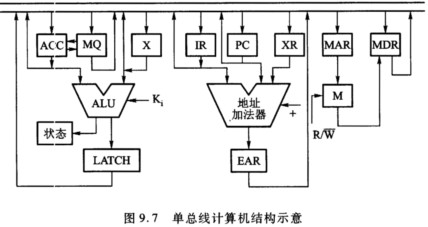

已知单总线计算机结构如图9.7所示,其中XR为变址寄存器,EAR为有效地址寄存器,LATCH为暂存器。假设

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“已知单总线计算机结构如图9.7所示,其中XR为变址寄存器,E…”相关的问题

更多“已知单总线计算机结构如图9.7所示,其中XR为变址寄存器,E…”相关的问题

说明: (1)ADD X,D指令字中x为变址寄存器XR,D为形式地址。 (2)寄存器的输入和输出均受控制信号控制,如PCi表示PC的输入控制信号,又如MDRo表示MDR的输出控制信号。 (3)凡是需要经过总线实现寄存器之间的传送,需在流程图中注明,如PC→Bus→MAR,相应的控制信号为PCo和MARi。

说明: (1)ADD X,D指令字中x为变址寄存器XR,D为形式地址。 (2)寄存器的输入和输出均受控制信号控制,如PCi表示PC的输入控制信号,又如MDRo表示MDR的输出控制信号。 (3)凡是需要经过总线实现寄存器之间的传送,需在流程图中注明,如PC→Bus→MAR,相应的控制信号为PCo和MARi。

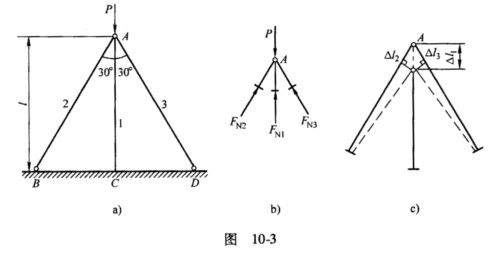

平面结构如图10-3a所示,已知其中的三根杆均为大柔度圆截面杆,且直径相等、材料相同。试分析其失稳破坏过程,并求出该结构的临界载荷Pcr。

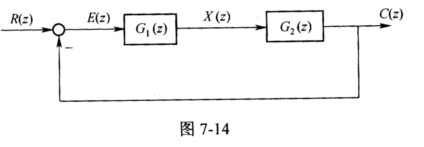

已知离散系统结构如图7-14所示。

其中:x(k)=x(k)-x(k-1),c(k)=1.5c(k-1)-5c(k-2)+4x(k-1)。试确定系统的脉冲传递函数G1(z)和G2(z)并判断系统的稳定性。

其中:x(k)=x(k)-x(k-1),c(k)=1.5c(k-1)-5c(k-2)+4x(k-1)。试确定系统的脉冲传递函数G1(z)和G2(z)并判断系统的稳定性。

结构受力如图9—1 6(a)所示。其中AB梁的弯曲刚度为EI,杆的截面积为A;二者材料相同,弹性模量均为E。若EI、A、l等均为已知,求BC杆所受的拉力。

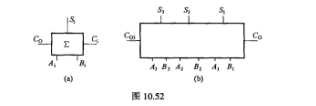

已知一位二进制全加器逻辑符号如图10.52(a)所示,进位输出表达式Co=G+P·Ci(其

中G=Ai·Bi,P=Ai+Bi),试求采用超前进位结构的三位二进制加法器(如图10.52(b)所示)的最高位进位输出表达式Co3.

高电平为读,低电平为写)。

已知该机存储器地址空间从0连续编址,其地址空间分配如下:最低8K为系统程序区,由ROM芯片组成;紧接着40K为备用区,暂不连接芯片;而后78K为用户程序和数据空间,用静态RAM芯片组成;最后2K用于I/O设备(与主存统一编址)。现有芯片如下:

SRAM:16K×8位,其中CS:为片选信号,低电平有效,WE:为写控制信号,低电平写,高电平读。

ROM:8K×8位,其中CS:为片选信号,低电平有效,OE:为读出控制,低电平读出有效。

译码器:3―8译码器,输出低电平有效;为使能信号,低电平时译码器功能有效。

其它“与、或”等逻辑门电路自选。

(1)请问该主存需多少SRAM芯片?

(2)试画出主存芯片与CPU的连接逻辑图。

(3)写出各芯片地址分配表。

已知电路形式如图题5.3.6(a)所示,其中管子输出特性如图题5.3.6(b)所示,电路参数为Rd=25kΩ,R=1.5kΩ,Rg=5MΩ,VDD=15V。试用图解法和计算法求静态工作点Q。