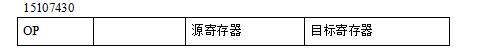

更多“指令格式如下所示,OP为操作码字段,试分析指令格式的特点。”相关的问题

更多“指令格式如下所示,OP为操作码字段,试分析指令格式的特点。”相关的问题

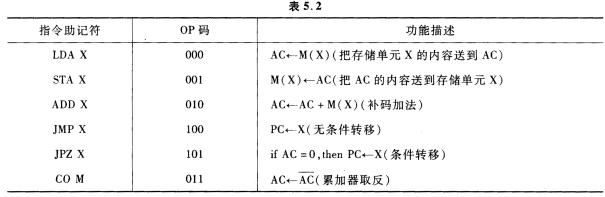

CPU的结构如图5.1所示,其中AC为累加器,AR为主存地址寄存器,DR为主存数据寄存器,DR(OP)为DR的操作码字段,DR(ADR)为DR的地址码字段,IR为指令寄存器,Pc为程序计数器。M为主存储器。表5.1列出CPU控制信号,表5.2列出指令组助记符及其功能,并给出每条指令的操作码。

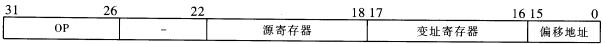

试设计:(1)满足所给条件的微指令格式(直接控制法)。 (2)设计表5?2中6条指令的微程序流程图,标明每条微指令在控制存储器中的地址。

试设计:(1)满足所给条件的微指令格式(直接控制法)。 (2)设计表5?2中6条指令的微程序流程图,标明每条微指令在控制存储器中的地址。

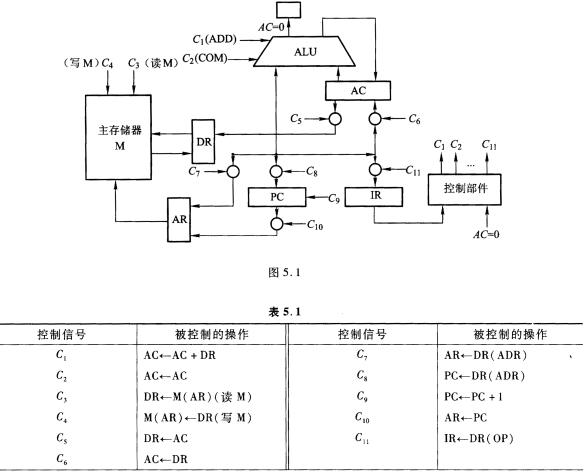

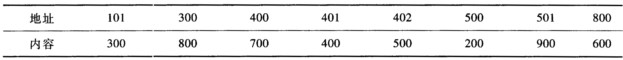

运算器结构如图6.23所示。IR为指令寄存器,R1~R3是3个通用寄存器,A和B是三选一多路选择器,数据通路的选择分别由AS0、AS1和BS0、BS1控制(如BS0BS1=01时选择R1,BS0BS1=10时选择R2,BS0BS1=11时选择R3)。S1、S2是操作性质控制端,功能如下:

S1S2=00时,ALU输出B

S1S2=01时,ALU输出A+B

S1S2=10时,ALU输出A-B

S1S2=11时,ALU输出

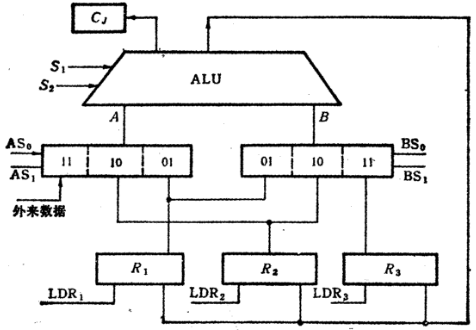

假设有以下4条机器指令,其操作码OP和功能如表6.2所示。

| 表6.2 4条机器指令的操作码OP和功能 | ||

| 指令名称 | OP | 指令功 能 |

| MOV ADD COM ADT | 00 01 10 11 | 从源寄存器传送一个数到目标寄存器 源寄存器内容与目标寄存器内容相加后送目标寄存器 源寄存器内容取反后送目标寄存器 十进制加法指令,修正量6假定在R3,a、b数在R1和R2 |

要求:

A.操作码字段外辅助操作字段的代码

B.操作码字段中用来进行指令分类的代码

C.指令格式中的操作码

D.一种指令优化技术,不同地址数指令可以具有不同的操作码长度

A.操作码字段中用来进行指令分类的代码

B.指令格式中不同字段设置的操作码

C.操作码字段外用来操作字段的代码

D.一种指令优化技术,即让操作码的长度随地址数的变化而变化

扩展操作码是________。

A.操作码字段以外的辅助操作字段的代码

B.指令格式中不同字段设置的操作码

C.一种指令优化技术,即让操作码的长度随地址数的减少而增加,不同地址数的指令可以具有不同的操作码长度

A.仅有一个操作数,其地址由指令的地址码提供;

B. 可能有一个操作数,也可能有两个操作数;

C. 一定有两个操作数,另一个是隐含的;

D. 指令的地址码字段存放的一定是操作码。

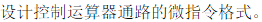

一条双字长的取数指令(LDA)存于存储器的100和101单元,其中第一个字为操作码和寻址特征M,第二个字为形式地址。假设PC当前值为100,变址寄存器XR的内容为100,基址寄存器的内容为200。存储器各单元的内容如下所示:

写出下列寻址方式的有效地址,以及取数指令执行结束后,累加器ACC的内容。 (1)直接寻址 (2)立即寻址 (3)间接寻址 (4)相对寻址 (5)变址寻址 (6)基址寻址

写出下列寻址方式的有效地址,以及取数指令执行结束后,累加器ACC的内容。 (1)直接寻址 (2)立即寻址 (3)间接寻址 (4)相对寻址 (5)变址寻址 (6)基址寻址

如果结果不匹配,请

如果结果不匹配,请