题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

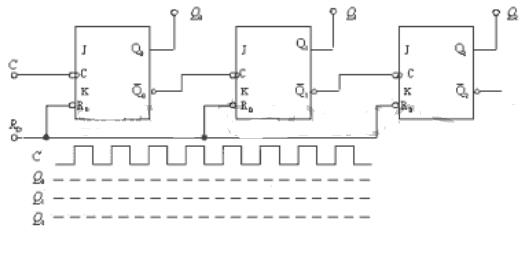

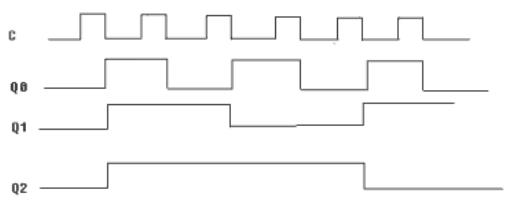

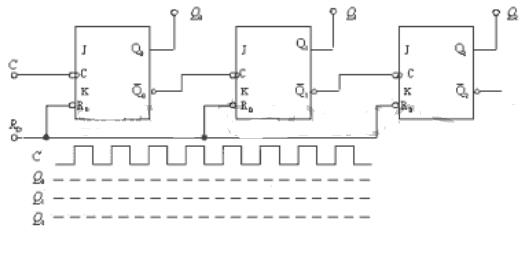

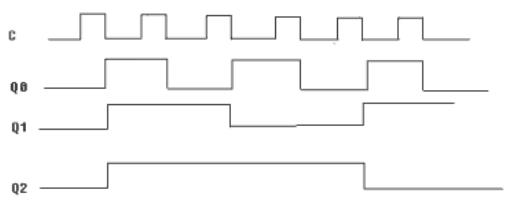

已知如图4.2.41所示逻辑电路及count、C脉冲波形,试画出输出Q0、Q1、Q2的波形(设Q0、Q1、Q2的初始状态均为“0”)。

已知如图4.2.41所示逻辑电路及count、C脉冲波形,试画出输出Q0、Q1、Q2的波形(设Q0、Q1、Q2的初始状态均为“0”)。

答案

答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

已知如图4.2.41所示逻辑电路及count、C脉冲波形,试画出输出Q0、Q1、Q2的波形(设Q0、Q1、Q2的初始状态均为“0”)。

答案

答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“已知如图4.2.41所示逻辑电路及count、C脉冲波形,试…”相关的问题

更多“已知如图4.2.41所示逻辑电路及count、C脉冲波形,试…”相关的问题

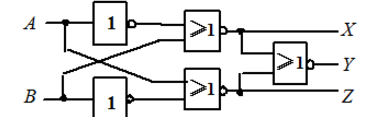

已知实现某逻辑功能的逻辑电路如图1-1所示,试写出其逻辑函数表达式,并用最少的与非门实现。

逻辑电路如图4.2.47所示,各触发器初始状态为“0”。已知CP、A、B的波形,试画出Q0、Q1和F的波形。

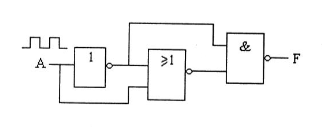

⑧逻辑电路如图8.25所示,已知输入波形A为脉冲信号,则输出F的波形( )。

A.与A同相的脉冲信号

A.与A同相的脉冲信号

B.与A反相的脉冲信号 C.高电平1

由一位全加器FA、2-4线译码器及与非门组成的逻辑电路如图4.2.2所示,试写出逻辑函数f(a,b,c,d)的最小项表达式。

1.jpg)

由与、或、非门组成的逻辑电路及输入信号如图2.3.2所示。 (1)当不考虑门的传输延迟时间时,求L端的输出电平。 (2)如果每个门的平均传输延迟时间均为8 ns,试画出L端的输出波形。

1.jpg)