题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

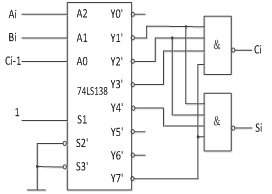

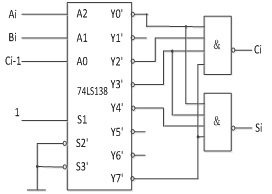

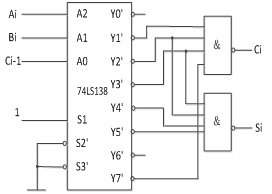

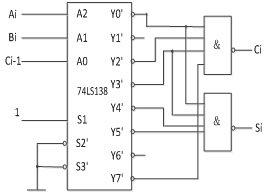

设计一个1位十进制数指示器,输入为8421BCD码,当输入数值大于5时输出为1: (1)用逻辑门设计电

设计一个1位十进制数指示器,输入为8421BCD码,当输入数值大于5时输出为1: (1)用逻辑门设计电路; (2)用VHDL语言设计电路。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

设计一个1位十进制数指示器,输入为8421BCD码,当输入数值大于5时输出为1: (1)用逻辑门设计电路; (2)用VHDL语言设计电路。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“设计一个1位十进制数指示器,输入为8421BCD码,当输入数…”相关的问题

更多“设计一个1位十进制数指示器,输入为8421BCD码,当输入数…”相关的问题

A.

B.

C.

D.

A.一组4位二进制数组成的BCD码只能表示1位十进制数

B.BCD码是一种人为选定的0~9的十个数字的代码

C.BCD码是一组4位二进制数,能表示16以内的任何一个十进制数

D.BCD码有多种

设机器数采用补码表示(含1位符号位),若寄存器内容为9BH,则对应的十进制数为()。

A.-27

B.-97

C.-101

D.155

设寄存器位数为8位,机器数采用补码形式(含1位符号位)。对应于十进制数-27,寄存器内容为________。

A.27H

B.9BH

C.E5H

设浮点数字长为16位(其中阶符1位,阶码5位,数符1位,尾数9位),对应十进制数-95的浮点规格化补码形式为________,若阶码采用移码,尾数采用补码,则机器数形式为________。