题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

基本RS触发器设计 实验要求 用原理图输入设计法或Verilog HDL文本输入设计法设计基本RS触发器电路,建立基

基本RS触发器设计

实验要求

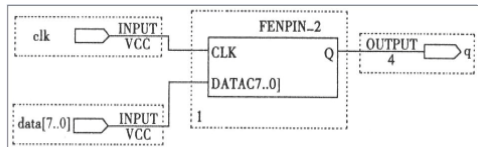

用原理图输入设计法或Verilog HDL文本输入设计法设计基本RS触发器电路,建立基本RS触发器的实验模式。通过电路仿真和硬件验证,进一步了解基本RS触发器的功能和特性。

设计原理

基本RS触发器可以由两个与非门或者两个或非门构成。由两个与非门构成的基本RS触发器的原理图如图所示,其中RDN是异步置0输入端,低电平有效;SDN是异步置1输入端,低电平有效;Q是触发器的输出端,QN是反相输出端。由图所示的电路可知,基本RS触发器的输出表达式为

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“基本RS触发器设计 实验要求 用原理图输入设计法或Veril…”相关的问题

更多“基本RS触发器设计 实验要求 用原理图输入设计法或Veril…”相关的问题