更多“由双4选1数据选择器组成的逻辑电路如图3.4.9所示,试写出…”相关的问题

更多“由双4选1数据选择器组成的逻辑电路如图3.4.9所示,试写出…”相关的问题

第1题

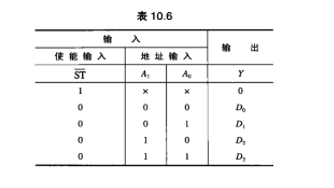

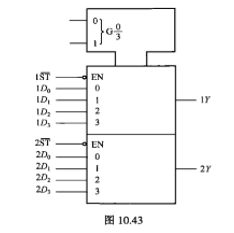

试用双4选1数据选择器74153和少量门设计一个有4个输入X3、X2、X1、X0和2个输出Y≇

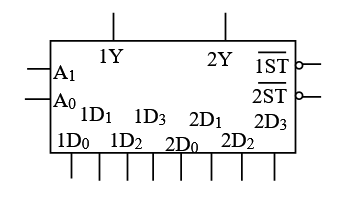

试用双4选1数据选择器74153和少量门设计一个有4个输入X3、X2、X1、X0和2个输出Y1、Y0的逻辑电路.电路输入为余3BCD码,输出为用2位二进制数表示的输入码中“1”的个数,例如,当输入X3X2X1X0=1010时,输出Y1Y0=10.当非余3码(伪码)输入时,要求输出Y1Y0=00.要求写出设计过程,画出电路图(规定X3、X2分别和数据选揮器地址码的高、低位相连接,74153的逻辑符号和功能表分别如图10.43和表10.6所示).

第3题

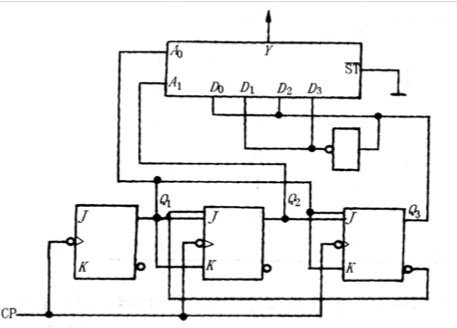

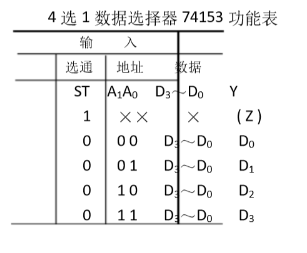

下图所示为双4选1数据选择器构成的组合逻辑电路,输入变量为A、B、C,输出F1、F2的逻辑函数分别为 、 ,其功能为 。

A.输出F1、F2的逻辑函数分别为 、 ,其功能为 。 #图片0$#

B.#图片1$#,#图片2$#,全加器

C.#图片3$#,#图片4$#,全减器

D.#图片1$#,#图片6$#,全加器

E.#图片7$#,#图片2$#,全减器

第4题

试用双4选1数据选择器74153设计一个全减器,它能完成二进制减法运算S=(A—B—C),CO为借位输出,写

试用双4选1数据选择器74153设计一个全减器,它能完成二进制减法运算S=(A—B—C),CO为借位输出,写

点击查看答案

出设计过程,画出逻辑电路。4选1数据选择器功能表和符号图分别见功能表和附图。

第6题

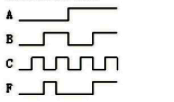

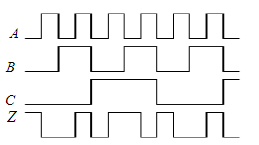

电路的输入(A、B、C)和输出(X、Y)波形如图A2-1所示,列出真值表,写出表达式,化简为最简式,分析其逻辑功能,并分

电路的输入(A、B、C)和输出(X、Y)波形如图A2-1所示,列出真值表,写出表达式,化简为最简式,分析其逻辑功能,并分别用基本逻辑门电路、4选1数据选择器(图A2-2)和3-8译码器(图A2-3)实现此逻辑电路。

第8题

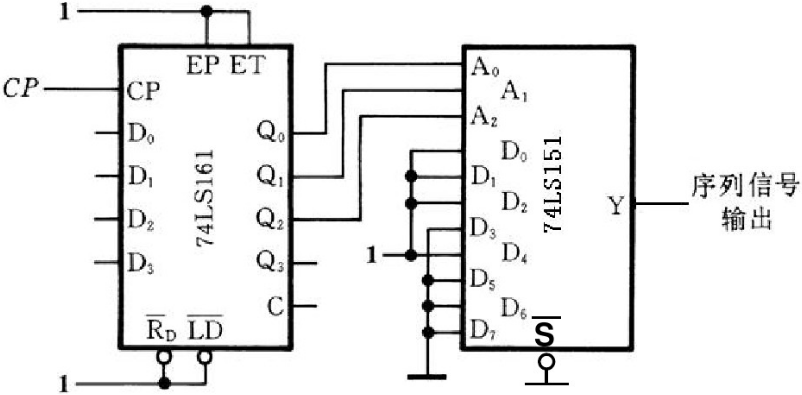

如图所示逻辑电路由CT74161(同步四位二进制计数器)和CT74151(八选一数据选择器)组成。

如图所示逻辑电路由CT74161(同步四位二进制计数器)和CT74151(八选一数据选择器)组成。

第9题

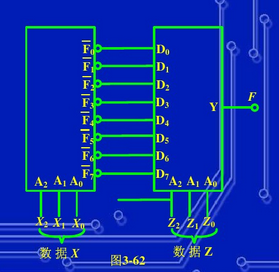

由输出低电平有效的3线-8线译码器和8选1数据选择器构成的电路如图4-20所示, (1)X2X1X0=Z2Z1Z0时,求输出F

由输出低电平有效的3线-8线译码器和8选1数据选择器构成的电路如图4-20所示,

(1)X2X1X0=Z2Z1Z0时,求输出F;

(2)X2X1X0≠Z2Z1Z0时,求输出F。

第10题

已知图3.2.103所示组合逻辑电路的输入和输出波形,试用一片4选1数据选择器实现此电路。要求:(1)写出输出函数Z

已知图3.2.103所示组合逻辑电路的输入和输出波形,试用一片4选1数据选择器实现此电路。要求:(1)写出输出函数Z的逻辑表达式:(2)画出逻辑线路图。

如果结果不匹配,请

如果结果不匹配,请