更多“用“与非”门实现以下逻辑关系,画出逻辑图:”相关的问题

更多“用“与非”门实现以下逻辑关系,画出逻辑图:”相关的问题

第2题

由双4选1数据选择器74LS153实现两个逻辑函数: F1(A,B,C,D)=∑m(0,3,5,6,9,10,12,15) F2(A,B,C,D)=∑m(0,1,2

由双4选1数据选择器74LS153实现两个逻辑函数:

F1(A,B,C,D)=∑m(0,3,5,6,9,10,12,15)

F2(A,B,C,D)=∑m(0,1,2,3,9,10,12,13,14,15)

画出设计后的逻辑图,并说明设计的过程。可使用其他逻辑门(与、或、非、异或),但要尽量少用。

第4题

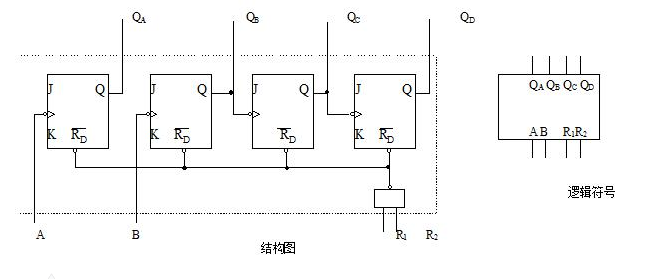

已知某集成计数器的结构图及逻辑符号如图所示,虚线以内为集成电路的内部电路。要求: (1)单片计数器能实现

已知某集成计数器的结构图及逻辑符号如图所示,虚线以内为集成电路的内部电路。要求:

(1)单片计数器能实现的最大模值为多少;

(1)单片计数器能实现的最大模值为多少;

(2)画出用该计数器实现五进制计数器的逻辑图;

(3)画出用该计数器实现六进制计数器的逻辑图;

(4)画出用该计数器实现三十进制计数器的逻辑图。

第5题

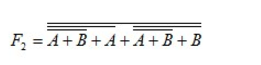

用卡诺图化简逻辑函数F(A,B,C,D)=∑m(8,9,12,13,14,15),请比较F的最简与或式和最简或与式,哪个更简单些?并用

用卡诺图化简逻辑函数F(A,B,C,D)=∑m(8,9,12,13,14,15),请比较F的最简与或式和最简或与式,哪个更简单些?并用相应的逻辑门电路实现其中更简单者,画出逻辑图。

第7题

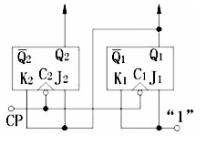

同步计数器设计 用JK下降沿触发器构成能够自启动的五进制同步计数器,已知状态转移过程的编码为:110→011→10

同步计数器设计

用JK下降沿触发器构成能够自启动的五进制同步计数器,已知状态转移过程的编码为:110→011→100→001→101→110,写出该触发器的状态方程、激励方程,画出该计数器的状态转移图和逻辑图(触发器输入可提供多输入相与功能,若需要外接逻辑门,使用与非门)。

第8题

用十进制数中规模计数器设计一个可控计数器,当控制信号X=0时为模6计数,X=1时为模8计数,计数状态可以自己选

择。说明设计过程,画出逻辑图。

以上设计可以使用外加的逻辑门。

下表是十进制中规模计数器的功能表。

| RESET | bar{LOAD} | CLK | QDQCQBQA |

| 1 | 1 | φ | 复位全0状态 |

| φ | 0 | ↑ | 预置 |

| φ | 1 | ↑ | 加计数 |

计数器还有进位输出F端,当加计数剑1001状态时产生进位负脉冲输出。

计数器的逻辑符号如图所示。

如果结果不匹配,请

如果结果不匹配,请

![画出用与非门和反相器实现下列函数的逻辑图。 [图]...画出用与非门和反相器实现下列函数的逻辑图。](https://img2.soutiyun.com/shangxueba/ask/17016001-17019000/17018880/b91392c-chaoxing2016-689559.jpeg)