题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

已知一位二进制全加器逻辑符号如图10.52(a)所示,进位输出表达式Co=G+P·Ci(其中G=Ai⌘

已知一位二进制全加器逻辑符号如图10.52(a)所示,进位输出表达式Co=G+P·Ci(其

中G=Ai·Bi,P=Ai+Bi),试求采用超前进位结构的三位二进制加法器(如图10.52(b)所示)的最高位进位输出表达式Co3.

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

已知一位二进制全加器逻辑符号如图10.52(a)所示,进位输出表达式Co=G+P·Ci(其

中G=Ai·Bi,P=Ai+Bi),试求采用超前进位结构的三位二进制加法器(如图10.52(b)所示)的最高位进位输出表达式Co3.

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“已知一位二进制全加器逻辑符号如图10.52(a)所示,进位输…”相关的问题

更多“已知一位二进制全加器逻辑符号如图10.52(a)所示,进位输…”相关的问题

由一位全加器FA、2-4线译码器及与非门组成的逻辑电路如图4.2.2所示,试写出逻辑函数f(a,b,c,d)的最小项表达式。

1.jpg)

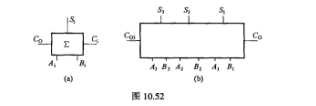

已知集成移位寄存器的逻辑符号功能表如图4-66(a)、(b)所示,试画出在图4-66(c)所示信号作用下Q7、

的输出波形。

的输出波形。

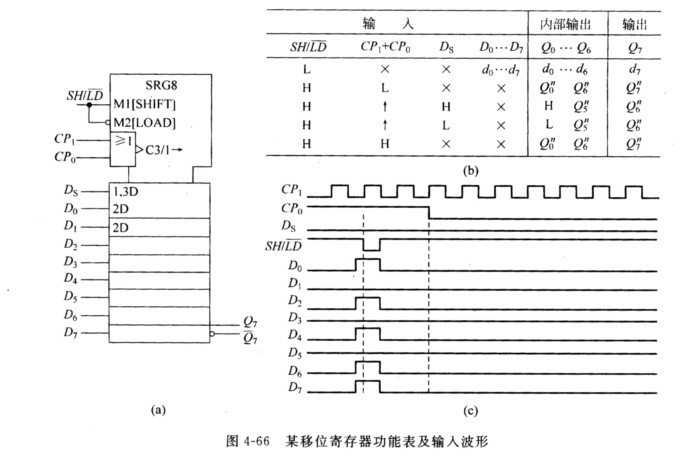

已知某十进制集成计数器的逻辑符号及功能表如图4-57(a)、(b)所示,试画出在图4-57(c)所示输入信号作用下Q0、Q1、Q2、Q3及

的输出波形。

的输出波形。

画出实现n位小数(不包括符号位在内)的补码一位乘运算器框图。要求: (1)指出寄存器和全加器位数; (2)详细画出最低位全加器的输入电路; (3)描述重复加和移位的操作; (4)指出加和移位次数。

设机器数字长为n位(不包括符号位),画出原码一位乘的运算器框图(图中必须反映原码一位乘算法),要求: (1)寄存器和全加器均用方框表示; (2)指出每个寄存器的位数及寄存器中操作数的名称; (3)详细画出第5位全加器的输入逻辑电路(设第n位为最低位); (4)描述原码一位乘法过程中的重复加和移位操作。

设机器数字长为n位(不包括符号位),画出补码一位乘的运算器框图(图中必须反映补码一位乘算法),要求: (1)寄存器和全加器均用方框表示; (2)指出每个寄存器的位数及寄存器中操作数的名称; (3)详细画出第5位全加器的输入逻辑电路; (4)描述补码一位乘法过程中的重复加和移位操作。

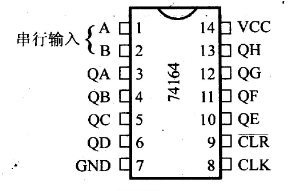

74164的符号图和功能表见图14和下表。逻辑电路如图15所示,其中RA、RB和RS均为74164,其余电路为全加器和D触发器,要求:

| bar{CR} | CP | D0=SASB | Q0Q1…Q7 |

| 0 | × | × | 0 0…0 |

| 1 | ↑ | 0 | 0 Q0…Q6 |

| 1 | ↑ | 1 | 1 Q0…Q6 |

(1)8个CP脉冲后,RA、RB和RS中的内容Q7Q6…Q0分别为?

(2)再来8个CP脉冲后,RA、RB和RS中的内容Q7Q6…Q0分别为?

(3)该电路实现了什么功能?

已知程序表10.5,分别写出组合逻辑控制部件和微程序控制部件所发出的全部微命令及节拍安排(指令地址和操作数地址均用十六进制数表示)。