题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

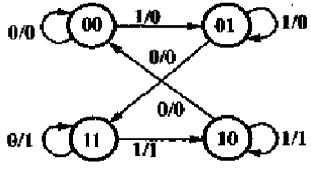

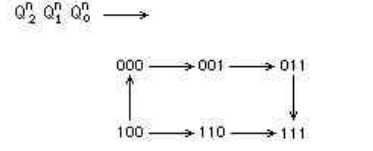

同步计数器设计 用JK下降沿触发器构成能够自启动的五进制同步计数器,已知状态转移过程的编码为:110→011→10

同步计数器设计

用JK下降沿触发器构成能够自启动的五进制同步计数器,已知状态转移过程的编码为:110→011→100→001→101→110,写出该触发器的状态方程、激励方程,画出该计数器的状态转移图和逻辑图(触发器输入可提供多输入相与功能,若需要外接逻辑门,使用与非门)。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“同步计数器设计 用JK下降沿触发器构成能够自启动的五进制同步…”相关的问题

更多“同步计数器设计 用JK下降沿触发器构成能够自启动的五进制同步…”相关的问题