题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[单选题]

一个8421BCD码十进制计数器,设其初态Q3Q2Q1Q0=0000,输入的时钟脉冲频率f=1kHz。试问在100ms时间内,共输入了多少个脉冲()?

A.10

B.100

C.1000

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A.10

B.100

C.1000

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“一个8421BCD码十进制计数器,设其初态Q3Q2Q1Q0=…”相关的问题

更多“一个8421BCD码十进制计数器,设其初态Q3Q2Q1Q0=…”相关的问题

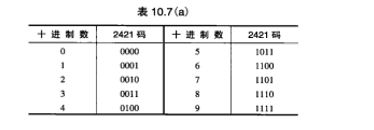

选择:一个十进制数79.25用8421BCD码表示为( )。

(A) 01111001.00100101

(B) 01001111.01000000

(C) 10110000.10111111

(D) 10110001.11000000

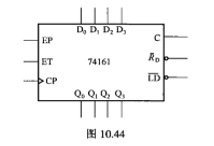

设计一个1位十进制数指示器,输入为8421BCD码,当输入数值大于5时输出为1: (1)用逻辑门设计电路; (2)用VHDL语言设计电路。

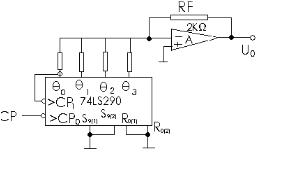

下图所示的电路中,计数器74LS290已接成5421BCD码十进制计数状态,θ0为最低位,θ3为最高位,设计数器输出的高电平为3.6V,低电平为0V。当θ3θ2θ1θ0时,求输出电压U0的值?